Altera FPGA– Bit Slip

2024-10-07 20:50:03

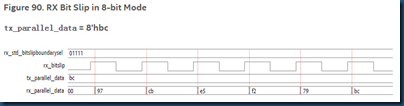

通过在接收端加延时,在延时间隙插入‘0’或‘1’,以使最终接收和期望数据一致。

BitSlip操作要注意几点:

1,BitSlip操作在rx_bitslip的上升沿即开始;

2,BitSlip操作开始后,必须等待至少2个平行信号的时钟周期后,才可开始检查数据是否对齐;因为需要2个时钟周期清除受损数据。

最新文章

- 关于MapReduce中自定义Combine类(一)

- MyEclipse中屏蔽js检验

- git的使用以及github

- jQuery原生框架-----------------dom操作

- 利用 druid 解析器解析SQL

- Struts2入门3 深入学习

- Telegram传奇:俄罗斯富豪、黑客高手、极权和阴谋…

- Jquery-EasyUI学习~

- 【转】Android各种Adapter的用法

- OSPF(Open Shortest Path First开放式最短路径优先 -链路状态路由协议

- android studio c++ 自动补全

- zabbix监控的基础概念、工作原理及架构

- Java线程与Linux内核线程的映射关系

- Centos6 iptables 防火墙设置【转】

- UVA315 Network 连通图割点

- Codeforces Round #487 (Div. 2) E. A Trance of Nightfall (矩阵优化)

- Java全栈程序员之03:Ubuntu下安装idea

- Ubuntu上安装git和创建工作区和提交文件!!!

- Python3学习之路~5.6 shutil & zipfile & tarfile模块

- bzoj3111: [Zjoi2013]蚂蚁寻路