【iCore1S 双核心板_FPGA】例程十六:基于SPI的ARM与FPGA通信实验

2024-08-26 13:45:25

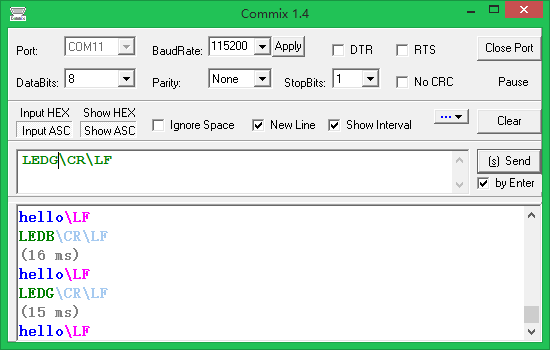

实验现象:

核心代码:

int main(void)

{

int i,n;

char buffer[];

char spi_buffer[]; HAL_Init();

system_clock.initialize(); led.initialize();

usart1.initialize();

spi.initialize(); usart1.printf("Hello! I am iCore1S!\r\n");

while()

{

if(usart1.receive_ok_flag)

{

usart1.receive_ok_flag = ;

for(i = ;i < ;i++)

{

buffer[i] = tolower(usart1.receive_buffer[i]);

}

n = strlen(buffer); if(memcmp(buffer,"ledr",strlen("ledr")) == )

{ LED_RED_ON;

LED_GREEN_OFF;

LED_BLUE_OFF;

}

if(memcmp(buffer,"ledg",strlen("ledg")) == )

{ LED_RED_OFF;

LED_GREEN_ON;

LED_BLUE_OFF;

}

if(memcmp(buffer,"ledb",strlen("ledb")) == )

{ LED_RED_OFF;

LED_GREEN_OFF;

LED_BLUE_ON;

}

buffer[]=;

n=strlen(buffer);

spi.write_nbyte(n,buffer);

for(i=;i<;i++)

{

spi_buffer[i] = spi.write_byte(0x00);

} usart1.printf("%s\n",spi_buffer);

}

}

}

module SPI(

input CLK_12M,

input spi_clk,

input spi_mosi,

input spi_cs,

output spi_miso, output FPGA_LEDR,

output FPGA_LEDG,

output FPGA_LEDB

); //-------------------------rst_n---------------------------//

/*复位信号*/

reg [:]rst_cnt = 'd0;

reg rst_n = 'd0; always @(posedge CLK_12M)

if(rst_cnt == 'd50)

begin

rst_n <= 'd1;

rst_cnt <= rst_cnt;

end

else rst_cnt <= rst_cnt + 'd1; //-------------------------parameter---------------------------//

parameter ledr = {'d108,8'd101,'d100,8'd114},

ledg = {'d108,8'd101,'d100,8'd103},

ledb = {'d108,8'd101,'d100,8'd98},

hello = {'d104,8'd101,'d108,8'd108,'d111}; //--------------------------spi_mosi---------------------------//

/*接收模块*/

reg [:]i;

reg [:]data_in;

reg [:]temp_data,data; always@(posedge spi_clk or negedge rst_n)

if(!rst_n)

begin

i <= 'd0;

temp_data <= 'd0;

data <= 'd0;

data_in <= 'd0;

end

else case(i) //从高位开始接收数据,每8个spi_clk时钟接收一个Byte

'd0:

begin

i <= i + 'd1;

data_in <= {data_in[:],spi_mosi};

temp_data <= {temp_data[:],data_in};

if(data_in == 'd13)

begin

data <= temp_data;

end

else

begin

data <= data;

end

end

'd1,4'd2,'d3,4'd4,'d5,4'd6:

begin

i <= i + 'd1;

data_in <= {data_in[:],spi_mosi};

end

'd7:begin

i <= 'd0;

data_in <= {data_in[:],spi_mosi};

end

default: i <= 'd0;

endcase //--------------------------data----------------------------//

/*对比接收数据*/

reg [:]led; always@(posedge CLK_12M or negedge rst_n)

if(!rst_n)

begin

led <= 'b111;

end

else if (data == ledr)

led <= 'b011; //红灯亮

else if (data == ledg)

led <= 'b101; //绿灯亮

else if (data == ledb)

led <= 'b110; //蓝灯亮 assign {FPGA_LEDR,FPGA_LEDG,FPGA_LEDB} = led; //--------------------------spi_miso----------------------------//

/*发送模块*/

reg [:]data_out;

reg [:]j;

reg MISO; always@(negedge spi_clk or negedge rst_n)

if(!rst_n)

begin

data_out <= hello;

j <= 'd0;

end

else case(j) //连续40个spi_clk_r时钟发送“hello”字符串

'd0:

begin

{MISO,data_out[:]} <= data_out;

j <= j + 'd1;

end

'd39:

begin

{MISO,data_out[:]} <= data_out;

data_out <= hello;

j <= 'd0;

end

default:

begin

{MISO,data_out[:]} <= data_out;

j <= j + 'd1;

end

endcase assign spi_miso = MISO; //--------------------------endmodule----------------------------//

endmodule

实验方法及指导书:

链接:http://pan.baidu.com/s/1jImpPRo 密码:c4s0

最新文章

- mac下 tomcat8+jdk1.8+servlet+Spring环境搭建中的问题

- 安卓解析json,使用BaseAdapter添加至ListView中,中间存储用JavaBean来实现

- quartz使用(一)

- 写好的mapreduce程序,编译,打包,得到最后的jar包! 验证jar包 ! 整体流程

- ASP.NET MVC 之 View 测试

- ios开发之网络基础

- Mysql Binlog 三种格式介绍及分析

- unity3d Find()使用

- 解决 jsp:include 引用文件时出现乱码的问题

- 屏幕适配基础——了解:ppi、dpi、px、sp、dp

- Entity Framework Core 懒加载

- 转载-Mac下iterm无法使用rz并提示waiting to receive.**B0100000023be50

- SQL 数据类型

- vue父组件给子组件传值:属性的形式

- 三种不同类型的ssh隧道

- Python3+SQLAlchemy+Sqlite3实现ORM教程

- Testing - 软件测试知识梳理 - 比较质量保证(QA)与质量控制(QC)

- 写一个function,清除字符串前后的空格。(兼容所有浏览器)

- 【高级算法】遗传算法解决3SAT问题(C++实现)

- 【转】每天一个linux命令目录