基于MATLAB2016b图形化设计自动生成Verilog语言的积分模块及其应用

2024-10-14 20:30:36

在电力电子变流器设备中,常常需要计算发电量,由于电力电子变流器设备一般是高频变流设备,所以发电量的计算几乎时实时功率的积分,此时就会用到一个积分模块。发电量计算的公式如下:Q=∫P。

FPGA由于其并行处理的运算方式,使其在电力电子领域的应用越来越广泛,有专家断言,DSP能做的事情,FPGA都可以做。

此外,MATLAB2016bb在图形化设计算法自动生成代码上做了大量优化,使算法开发的时间大大缩小,下面共享一个基于MATLAB2016b图形化设计自动生成Verilog语言的积分模块及其应用。

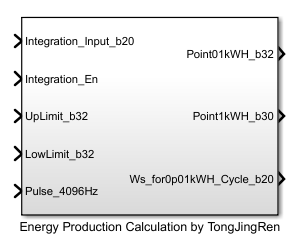

1 在MATLAB2016b中吗,模块的封装如下图所示。

接口定义如下:

Integration_Input_b20——需要积分的量,比如在电力电子变流设备中的有功功率P,单位位W,是一个20位宽的有符号数,范围[-2^(19),(2^19-1)];

Integration_En——积分使能信号,仅该位置1模块方进行积分运算。

UpLimit_b32 和 LowLimit_b32——积分上限与下限限制,位宽位32的有符号数。

Pulse_4096Hz——该脉冲频率是积分频率,即1s时间内积分4096次,则可以满足时时积分要求。

Point01kWH_b32——发电量单位:0.01度(1度=1kW*H)。

Point1kWH_b30——发电量单位:0.1度(1度=1kW*H)。

Ws_for0p01kWH_Cycle_b20——该位主要观察在0.01度的周期内来回显示时时电量,每0.01度就刷新一次。

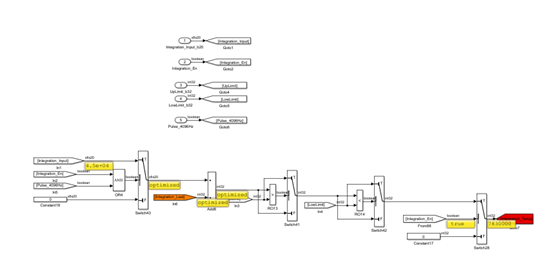

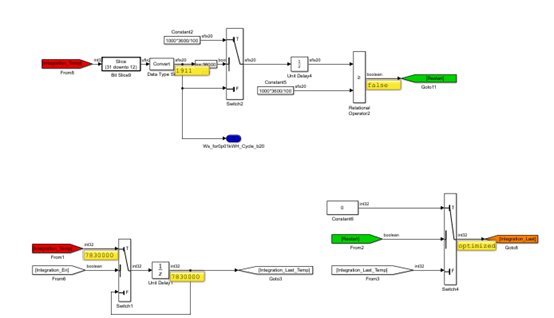

2 在MATLAB2016b中吗,模块并行图形化设计如下图所示。

3 在MATLAB2016b中自动生成可应用的Verilog语言代码如下:

// -------------------------------------------------------------

//

// File Name: F:\TongJingRen\Energy Production Calculation by TongJingRen\Simulation_Model_Base_Platform20180211\Energy_Production_Calculation_by_TongJingRen.v

// Created: 2018-02-27 11:32:09

//

// Generated by MATLAB 9.1 and HDL Coder 3.9

//

//

// -- -------------------------------------------------------------

// -- Rate and Clocking Details

// -- -------------------------------------------------------------

// Model base rate: 6.4e-07

// Target subsystem base rate: 6.4e-07

//

// ------------------------------------------------------------- // -------------------------------------------------------------

//

// Module: Energy_Production_Calculation_by_TongJingRen

// Source Path: Simulation_Model_Base_Platform20180211/Energy Production Calculation by TongJingRen

// Hierarchy Level: 0

//

// ------------------------------------------------------------- `timescale 1 ns / 1 ns module Energy_Production_Calculation_by_TongJingRen

(

g_clk,

Rst_n,

Integration_Input_b20,

Integration_En,

UpLimit_b32,

LowLimit_b32,

Pulse_4096Hz,

Point01kWH_b32,

Point1kWH_b30,

Ws_for0p01kWH_Cycle_b20

); input g_clk;

input Rst_n;

input signed [19:0] Integration_Input_b20; // sfix20

input Integration_En;

input signed [31:0] UpLimit_b32; // int32

input signed [31:0] LowLimit_b32; // int32

input Pulse_4096Hz;

output signed [31:0] Point01kWH_b32; // int32

output signed [29:0] Point1kWH_b30; // sfix30

output signed [19:0] Ws_for0p01kWH_Cycle_b20; // sfix20 wire OR4_out1;

wire switch_compare_1;

wire signed [19:0] Switch43_out1; // sfix20

reg signed [31:0] Unit_Delay1_out1; // int32

wire signed [31:0] Switch28_out1; // int32

wire signed [31:0] Switch1_out1; // int32

wire Relational_Operator2_relop1;

wire signed [31:0] Switch4_out1; // int32

wire signed [31:0] Add8_1; // sfix32

wire signed [31:0] Add8_out1; // int32

wire RO13_relop1;

wire signed [31:0] Switch41_out1; // int32

wire RO14_relop1;

wire signed [31:0] Switch42_out1; // int32

wire [19:0] Bit_Slice9_out1; // ufix20

wire signed [19:0] Data_Type_S6_out1; // sfix20

wire CT1_out1;

wire signed [19:0] Switch2_out1; // sfix20

reg signed [19:0] Unit_Delay4_out1; // sfix20

reg signed [31:0] Unit_Delay3_out1; // int32

wire signed [31:0] Add1_out1; // int32

wire signed [31:0] Switch3_out1; // int32

wire signed [40:0] Divide_out1; // sfix41

wire [29:0] Bit_Slice1_out1; // ufix30

wire signed [29:0] Data_Type_S1_out1; // sfix30 assign OR4_out1 = Integration_En & Pulse_4096Hz; assign switch_compare_1 = OR4_out1 > 1'b0; assign Switch43_out1 = (switch_compare_1 == 1'b0 ? 20'sb00000000000000000000 :

Integration_Input_b20); assign Switch1_out1 = (Integration_En == 1'b0 ? Unit_Delay1_out1 :

Switch28_out1); always @(posedge g_clk)

begin : Unit_Delay1_process

if (Rst_n == 1'b0) begin

Unit_Delay1_out1 <= 32'sb00000000000000000000000000000000;

end

else begin

Unit_Delay1_out1 <= Switch1_out1;

end

end assign Switch4_out1 = (Relational_Operator2_relop1 == 1'b0 ? Unit_Delay1_out1 :

32'sb00000000000000000000000000000000); assign Add8_1 = {{12{Switch43_out1[19]}}, Switch43_out1};

assign Add8_out1 = Add8_1 + Switch4_out1; assign RO13_relop1 = Add8_out1 > UpLimit_b32; assign Switch41_out1 = (RO13_relop1 == 1'b0 ? Add8_out1 :

UpLimit_b32); assign RO14_relop1 = Switch41_out1 < LowLimit_b32; assign Switch42_out1 = (RO14_relop1 == 1'b0 ? Switch41_out1 :

LowLimit_b32); assign Switch28_out1 = (Integration_En == 1'b0 ? 32'sb00000000000000000000000000000000 :

Switch42_out1); assign Bit_Slice9_out1 = Switch28_out1[31:12]; assign Data_Type_S6_out1 = Bit_Slice9_out1; assign CT1_out1 = Data_Type_S6_out1 >= 20'sb00001000110010100000; assign Switch2_out1 = (CT1_out1 == 1'b0 ? Data_Type_S6_out1 :

20'sb00001000110010100000); always @(posedge g_clk)

begin : Unit_Delay4_process

if (Rst_n == 1'b0) begin

Unit_Delay4_out1 <= 20'sb00000000000000000000;

end

else begin

Unit_Delay4_out1 <= Switch2_out1;

end

end assign Relational_Operator2_relop1 = Unit_Delay4_out1 >= 20'sb00001000110010100000; assign Add1_out1 = 32'sb00000000000000000000000000000001 + Unit_Delay3_out1; assign Switch3_out1 = (Relational_Operator2_relop1 == 1'b0 ? Unit_Delay3_out1 :

Add1_out1); always @(posedge g_clk)

begin : Unit_Delay3_process

if (Rst_n == 1'b0) begin

Unit_Delay3_out1 <= 32'sb00000000000000000000000000000000;

end

else begin

Unit_Delay3_out1 <= Switch3_out1;

end

end assign Point01kWH_b32 = Unit_Delay3_out1; assign Divide_out1 = Unit_Delay3_out1 * 9'sb011001101; assign Bit_Slice1_out1 = Divide_out1[40:11]; assign Data_Type_S1_out1 = Bit_Slice1_out1; assign Point1kWH_b30 = Data_Type_S1_out1; assign Ws_for0p01kWH_Cycle_b20 = Data_Type_S6_out1; endmodule // Energy_Production_Calculation_by_TongJingRen

最新文章

- js封装用户选项传递给Servlet之考试系统二

- eAccelerator、memcached、xcache、APC 等四个加速扩展的区别

- Error Domain=NSOSStatusErrorDomain Code=1718449215 "The operation couldn’t be completed. (OSStatus error 1718449215.)"

- iOS开发 iOS10推送必看

- javabean、DTO、VO

- 移动端-弹窗demo

- linux问题: 切换用户之后变成-bash-4.1$

- 二十四、oracle pl/sql 变量

- Jenkins安装后无法安装插件

- oracle11g处理空表

- [ERROR] Failed to execute goal org.codehaus.mojo:gwt-maven-plugin:2.5.0-rc1:compile (default) on project zeus-web: Command 解决

- Nginx proxy开启cache缓存

- UVA 10256 The Great Divide(点在多边形内)

- 【IDEA】【3】操作使用

- Win10安装mysql-8.0.11-winx64详细步骤

- shutdown&&isTerminated

- CodeForces - 1042B

- mail发邮件报错 "send-mail: fatal: parameter inet_interfaces: no local interface found for ::1"

- X-009 FriendlyARM tiny4412 uboot移植之SD Card用起来Kernel boot起来

- C语言中内存分配