HDL之Bitwise operation

1 Verilog

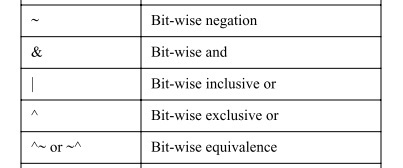

1.1 Bitwise operator

Bitwise operators perform a bit wise operation on two operands.

They take each bit in one operand and perform the operation with the corresponding bit in the other operand.

If one operand is shorter than the other, it will be extended on the left side with zeroes to match the length of the longer operand.

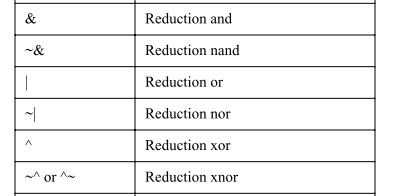

1.2 Reduction operator

Reduction operators are unary.

They perform a bit-wise operation on a single operand to produce a single bit result.

Reduction unary NAND and NOR operators operate as AND and OR respectively, but with their outputs negated.

2 VHDL

FUNCTION and_reduce (arg : STD_LOGIC_VECTOR) RETURN STD_LOGIC;

-- Result subtype: STD_LOGIC.

-- Result: Result of and'ing all of the bits of the vector.

function nand_reduce (arg : std_logic_vector )

return std_logic is

begin

return not and_reduce (arg);

end;

Others are nand_reduce, or_reduce, nor_reduce, xor_reduce, xnor_reduce

最新文章

- AtomicBoolean使用

- Entity Framework学习笔记——配置EF

- 两个APP之间怎么调用《IT蓝豹》

- PHP isset() 检测变量是否设置

- oralce闪回

- 自定义View的封装

- 链表中LinkList L与LinkList *L 借鉴

- SSM三大框架整合详细教程(Spring+SpringMVC+MyBatis

- Java的演化-Java8实战笔记

- MT【321】分类线性规划

- 阿里四不像Fourinone

- PostgreSQL主备流复制机制

- px 和 em 的区别

- 【POJ2409】Let it Bead Pólya定理

- UVALive 5846 计数

- django url 路由设置技巧

- mysql 匹配 findinset

- 【WPF/C#】使用BackgroundWorker实现多线程/异步操作

- SVN checkout 出的项目在PHPstorm中打开没有subversion(SVN)选项按钮怎么办?

- Jenkins Pipeline+Maven+Gitlab持续集成构建问题集锦