FPGA噪声干扰

在FPGA高速AD采集设计中,PCB布线差会产生干扰。今天小编为大家介绍一些布线解决方案。

1、信号线的等长

以SDRAM或者DDRII为例,数据线,命令线,地址线以及时钟线最好等长,误差不要超过500mil。

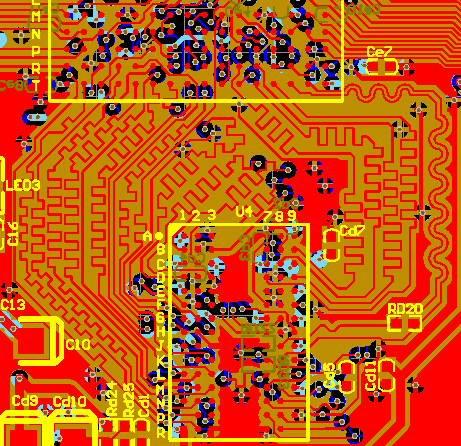

上图是FPGA与SDRAM布线,时钟频率设定为125M,为了等长可以走蛇形线。

蛇形走线虽然可以做到走线等长,但同时也占用更多的PCB面积。蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。

DDRII线路等长设计,最右边的弧度较大的走线为差分的时钟线,时钟线质量要求是比较高的。

布线是痛苦的,也是繁琐的,布不通时需要重新布线,不厌其烦的尝试,才能做出更好的效果。

2、电源芯片的选择

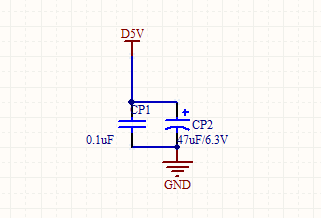

很多高速AD场合,开关电源并不合适,因为开关电源带来很多毛刺。大多数选择线性稳压电源。小编以ASM1117为例为大家介绍电源芯片中电容的使用。

5V电源输入端,应加容值较大的钽电容或者电解电容滤除电源的低频噪声,加104(0.1uF)瓷片电容滤除高频噪声。电源走线应适当加宽。

在PCB布线时,也应该在5V走线的末端加容值较大的电容。

以ASM1117-3.3降压为例,如下图:

如上图,1117的3.3输出走线往下走,那么电容CP5放在旁边是没有任何效果的,通常这种电容是104瓷片电容,这个电容的容值是一个非常好的容值,在电源滤波中效果非常好。

那么该如何布局?

如上图,此种布局,CP28以及 CP10放置,电容应当放在电源走线路径上。注意电容不能离芯片引脚太远,电容有滤波半径,超出某一范围,电容将起不到滤波效果。

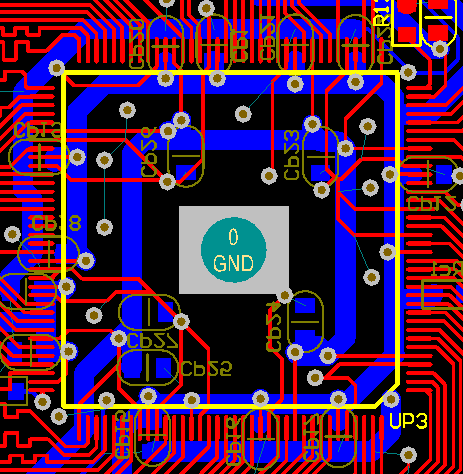

FPGA电源布线,根据多年布线经验以及产品稳定性,小编为大家推荐以下方案:

以QFP封装的FPGA为例,有三种电源,1.2V,2.5V,3.3V。布线时最好如上图效果,电源线之间最好隔开距离,FPGA电源引脚要加入104电容。

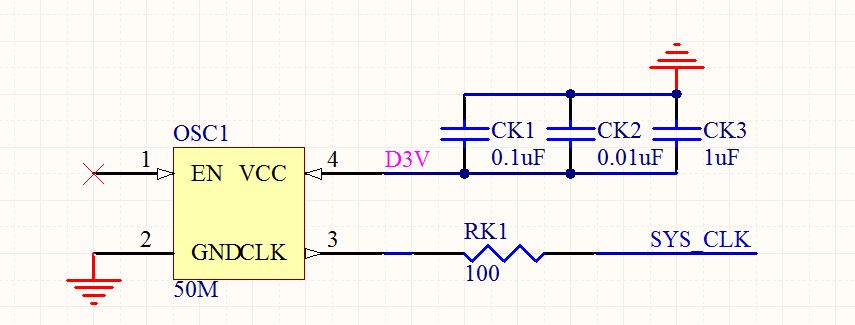

3、有源晶振布线

原理图设计如上,时钟输出端串入100~330欧姆的电阻,防止阻抗不匹配时时钟信号反射叠加。

有源晶振电源端加入103、104、105三种瓷片电容滤波,防止电源噪声和时钟之间的串扰。

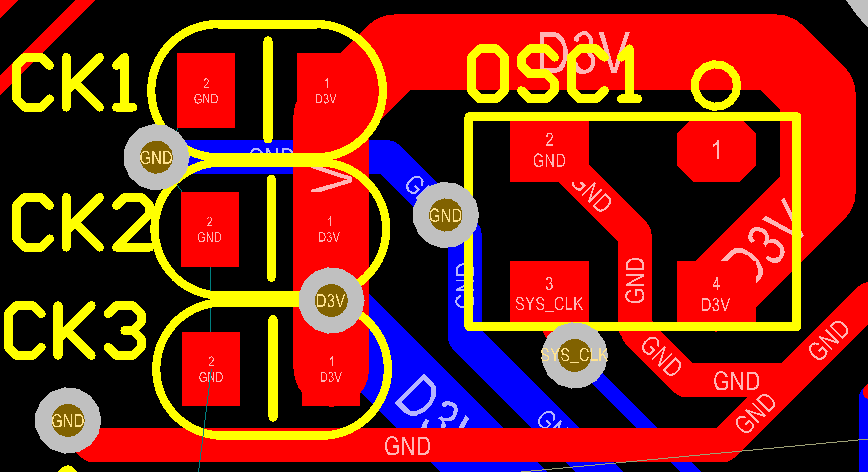

PCB布线时,上述效果时很糟糕的。晶振下面不应布线,电源走线应远离时钟线布线,并且中间加宽地线耦合,防止干扰。

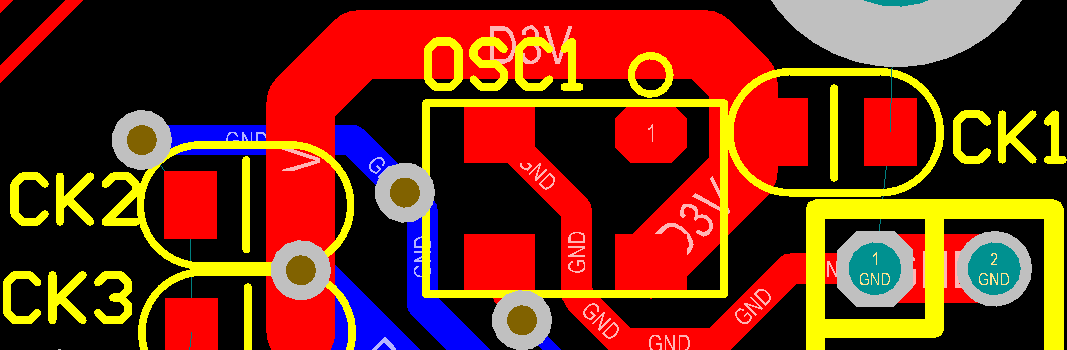

如上图布线,电源线避开时钟线,中间加入粗地线,注意有些地线不需要手动连接,放置地过孔,在铺铜(地网络)时,会自动加入。

此种方式放置电容亦可行。

最新文章

- Node.js-Socket.IO【1】-身份验证

- HTML 基础

- C# Dictionary 的几种遍历方法

- python 大数据分析

- C#设计模式——抽象工厂模式(Abstract Factory Pattern)

- 3.4html学习笔记之表格

- 最短路径算法——Dijkstra,Bellman-Ford,Floyd-Warshall,Johnson

- 过程化开发2048智力游戏WebApp

- Oracle的用户,权限以及角色

- 如果以一个树状的形式返回一个UIView的所有子视图

- 壁虎书6 Decision Trees

- OdnShop 发布 V1.0 正式版,完整可用的开源微商城系统

- 线程锁(互斥锁Mutex)及递归锁

- kindeditor用法简单介绍(转)

- 几道cf水题

- dh

- 深入理解C语言的函数调用过程 【转】

- JAVA解压文件

- Winfrom Panel Scroll End 的实现

- 五句话搞定JavaScript作用域【转】