[原创][FPGA][IP-Core]altlvds_tx & altlvds_rx

2024-08-30 05:16:02

1. 概述

Alter公司的QuartusII软件提供了LVDS发送和接收的IP核供我们使用,其在本质上可以理解为并行-串行数据的转换器。其在官方文档(见附件)上也这样说过。其中的应用场景有告诉AD/DA的数据传输等。

那在此我们就针对这一IP核进行了解、熟悉和测试。首先我们来对差分发送端进行学习。

2. altlvds_tx

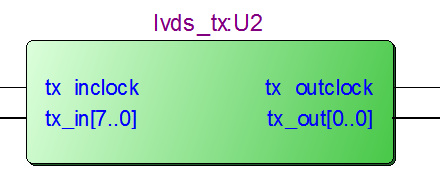

图2.1所示为一个简单的差分发送端,其有两个输入,一个为输入时钟,一个为输入数据。两个输出为穿行输出数据和输出时钟。

图2.1 altlvds_tx的RTL视图

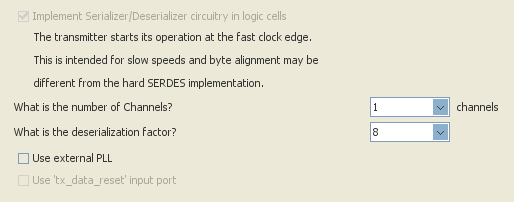

下面进入IP核配置部分,对主要的一些参数进行介绍说明。首先图2表示了其设置参数,图2.1中的number of channels(C)是通道数目,表示一共有多少通道的差分数据,例如C=4时,对应就为tx_out[3:0]。deserialization factor(J)表示串并参数,例如J=8,C=1时,对应为tx_in[7:0];J=8,C=2时,对应为tx_in[15:0]。

图2.2 通道数目和并行长度参数

下面为输出比特率和工作频率的设置,其应满足一定的规则,比如在本例中,串并参数J=8,那么应该有80Mbps=10MHz*8bit。此处应保持一定的一致。

图2.3,输出比特率和工作频率

输出时钟时钟设置与否,根据divide factor(B)来限定输出时钟的频率特性。下图中的B=2表示了输出时钟tx_outclk频率为模块输入时钟频率的一半。

图2.4,勾选输出时钟和设置分频参数

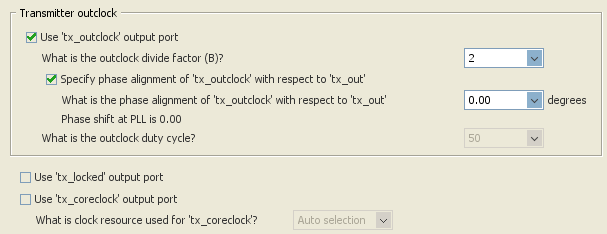

在规定完上述的参数设置后,进行波形的仿真,从中模块的四个输入输出可以看出该模块的具体功能。

图2.5 仿真波形图结果

3. altlvds_rx

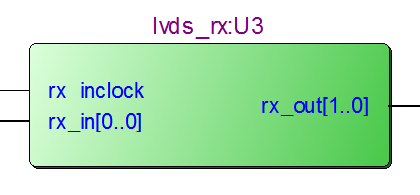

图3.1为一个简单的差分接收端,其有两个输入,一个输入时钟,一个输入数据。一个输出为输出并行数据。

图3.1 altlvds_rx的RTL视图

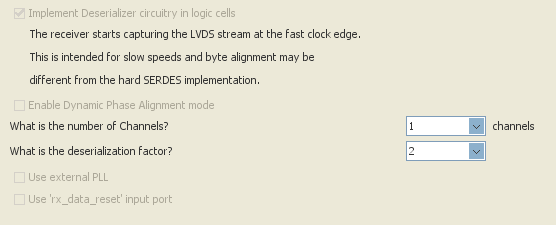

下面进入IP核配置部分,对串并参数J进行设置,下图中是将J设置为J=2。

图3.2 并串转换输出因子

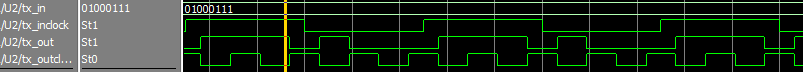

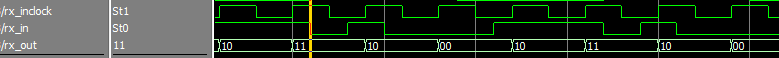

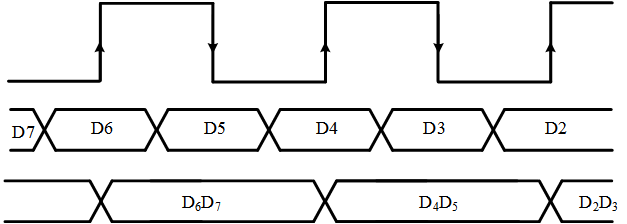

图3.3为仿真结果,从图中看出输入数据为循环序列01000111,其由接收器接收,每次在一个时钟周期内接收两个字节。从仿真结果中看出,就收为低位在前。原序列接收为10,00,10,11。且每次接收数据为时钟下降沿和时钟的当前上升沿。如图3.4所示。

图3.3 仿真波形图结果

.png)

图3.4 从上到下依次为输入时钟,输入数据,输出数据

最新文章

- DotNet项目中的一些常用验证操作

- Java中分割字符串

- Bing Map

- MyCat 学习笔记 第八篇.数据分片 之 求摸运算分片

- php和AJAX用户注册演示程序

- 一个关于正整数x的约数个数的结论

- hdu 4419 Colourful Rectangle

- Day1_PHP快速入门

- 计算数据库中30天以内,30-60天,60-90天,90天以外的数据的个数(用sql实现)

- 解决clipboard手机端无法复制的一种思路

- UUID.randomUUID().toString() 的作用

- Oracle聚合函数

- 搭建Elasticsearch平台

- eclipse中使用svn提交,更新代码。

- AnguarJS中链式的一种更合理写法

- POJ 2234 Matches Game(Nim博弈裸题)

- CM记录-CDH大数据平台实施经验总结2016(转载)

- First normal formal Second normal form

- Codeforces 908 D.New Year and Arbitrary Arrangement (概率&期望DP)

- bzoj 4871: [Shoi2017]摧毁“树状图”

热门文章

- destoon 给超级管理员系统权限(管理员管理,日志管理等)

- Linux 用户管理(二)

- ultraedit编辑器破解版下载

- python-matplotlib-lec0

- Linux学习-SRPM 的使用 : rpmbuild (Optional)

- Linux学习-systemctl 针对 timer 的配置文件

- Leetcode207--->课程表(逆拓扑排序)

- 【JavaScript】关于 eval()执行JavaScript语句的一次实验测试

- 【LeetCode】Binary Tree Preorder Traversal(二叉树的前序遍历)

- String、StringBuffer和StringBuilder,定义一个自己的StringBuilder的类