关于FIFO memory buffer模块的设计

2024-10-13 07:33:45

关于FIFO memory buffer模块的设计

FIFO memory

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/10/26 13:28:35

// Design Name:

// Module Name: fifomem

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// `include "block_define.v" module fifomem #(

parameter DATASIZE = , //Memory data word width

parameter ADDRSIZE = ) //Number of mem address bits depth = 16

( input [DATASIZE- : ] wdata,

input [ADDRSIZE- : ] waddr,

input wclken,

input wfull,

input wclk, input [ADDRSIZE- : ] raddr,

output [DATASIZE- : ] rdata

); //------------------------------------------------------------------------ `ifdef VENDORRAM // instantiation of a vendor's dual-port RAM blk_mem_gen_0 mem (

.clka(wclk), // input wire clka

.ena(wclken), // input wire ena

.wea(~wfull), // input wire [0 : 0] wea

.addra(waddr), // input wire [3 : 0] addra

.dina(wdata), // input wire [7 : 0] dina

.clkb(wclk), // input wire clkb

.addrb(raddr), // input wire [3 : 0] addrb

.doutb(rdata) // output wire [7 : 0] doutb

); `else

// RTL Verilog memory model localparam DEPTH = <<ADDRSIZE;

reg [DATASIZE- : ] mem[ : DEPTH-]; assign rdata = mem[raddr]; always @(posedge wclk)

if(wclken && !wfull)

mem[waddr] <= wdata; `endif endmodule

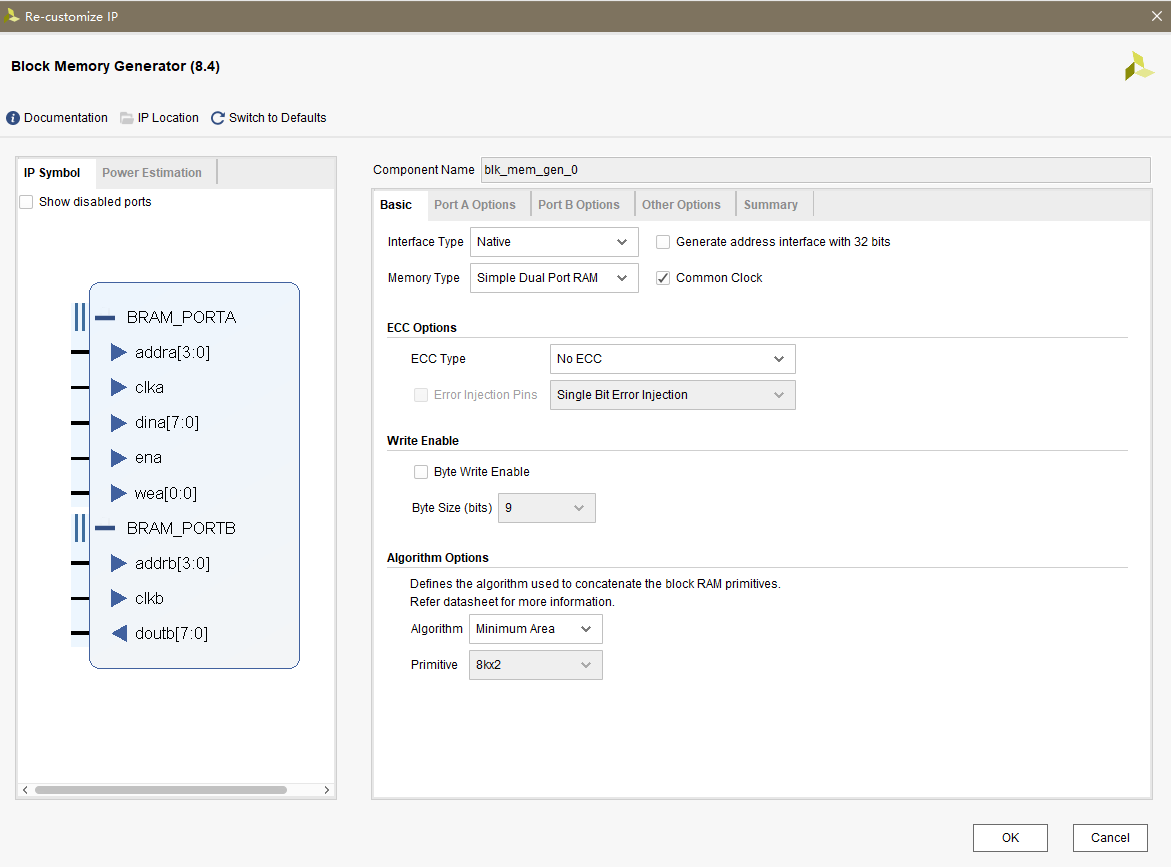

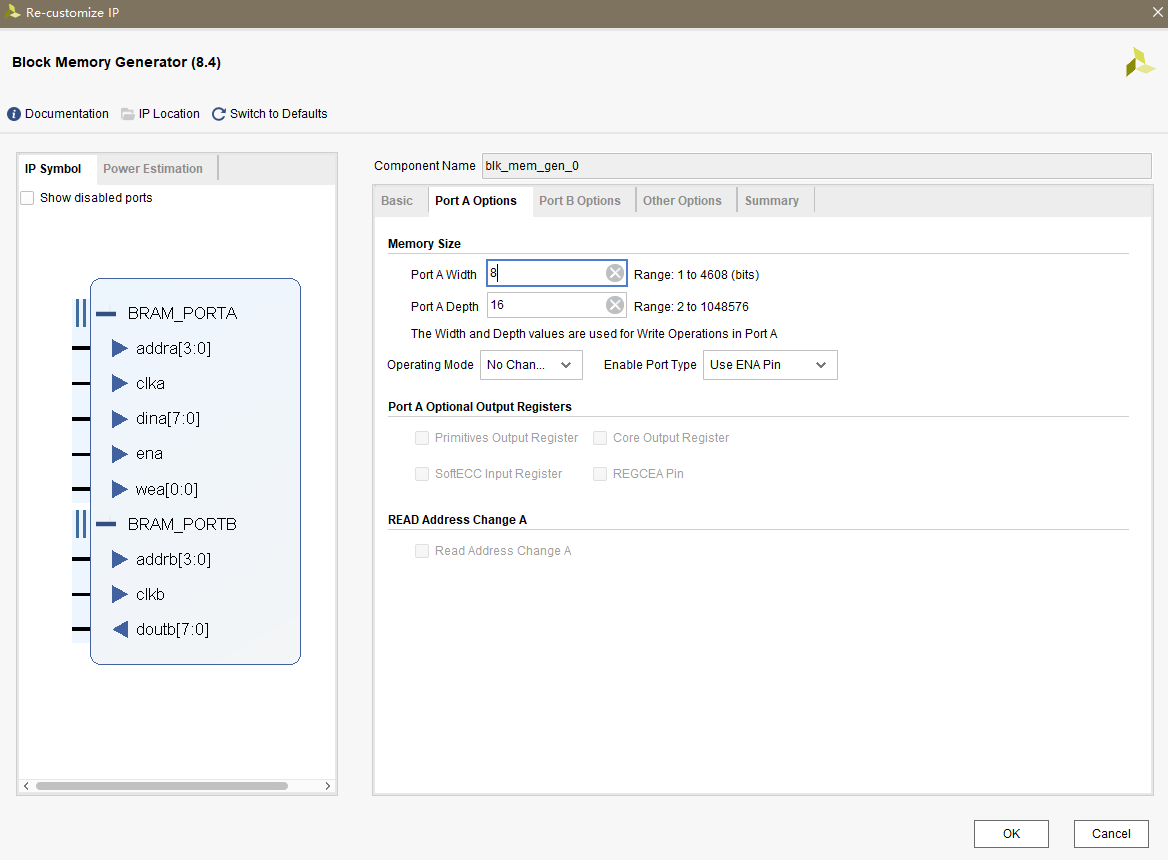

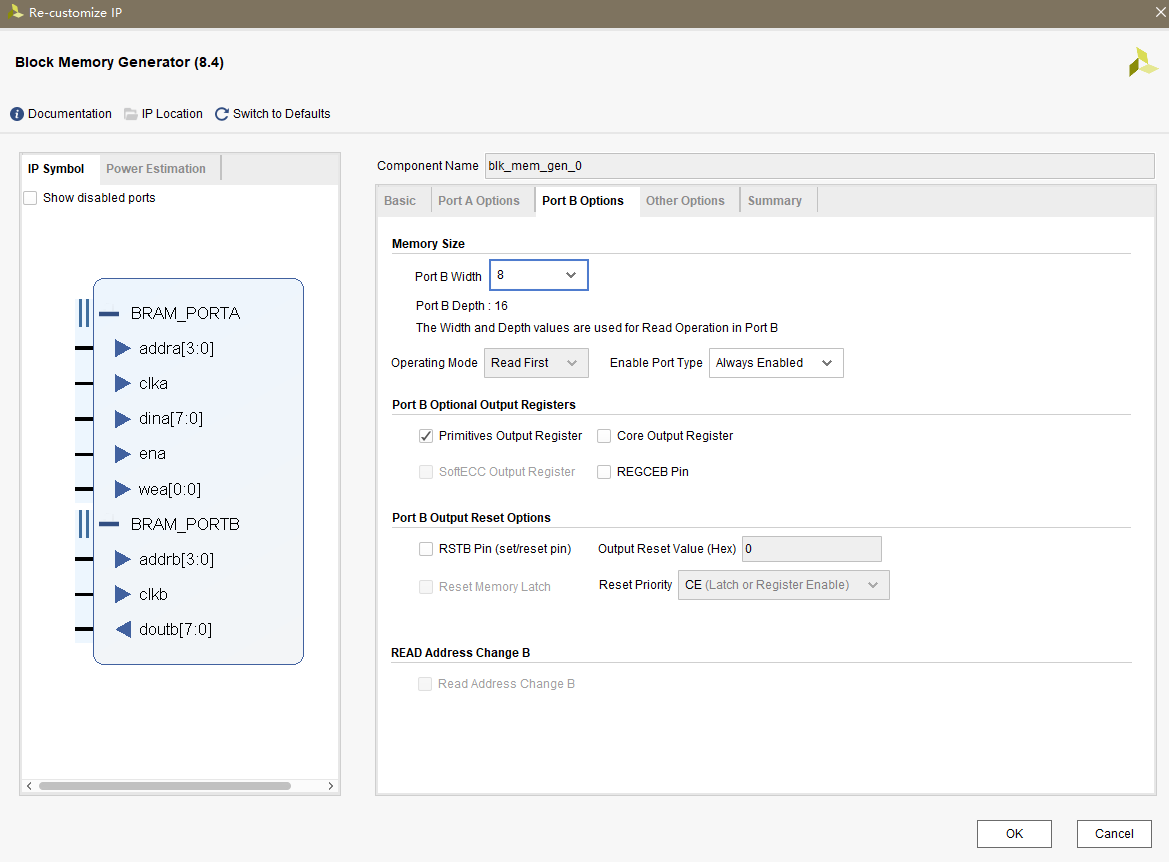

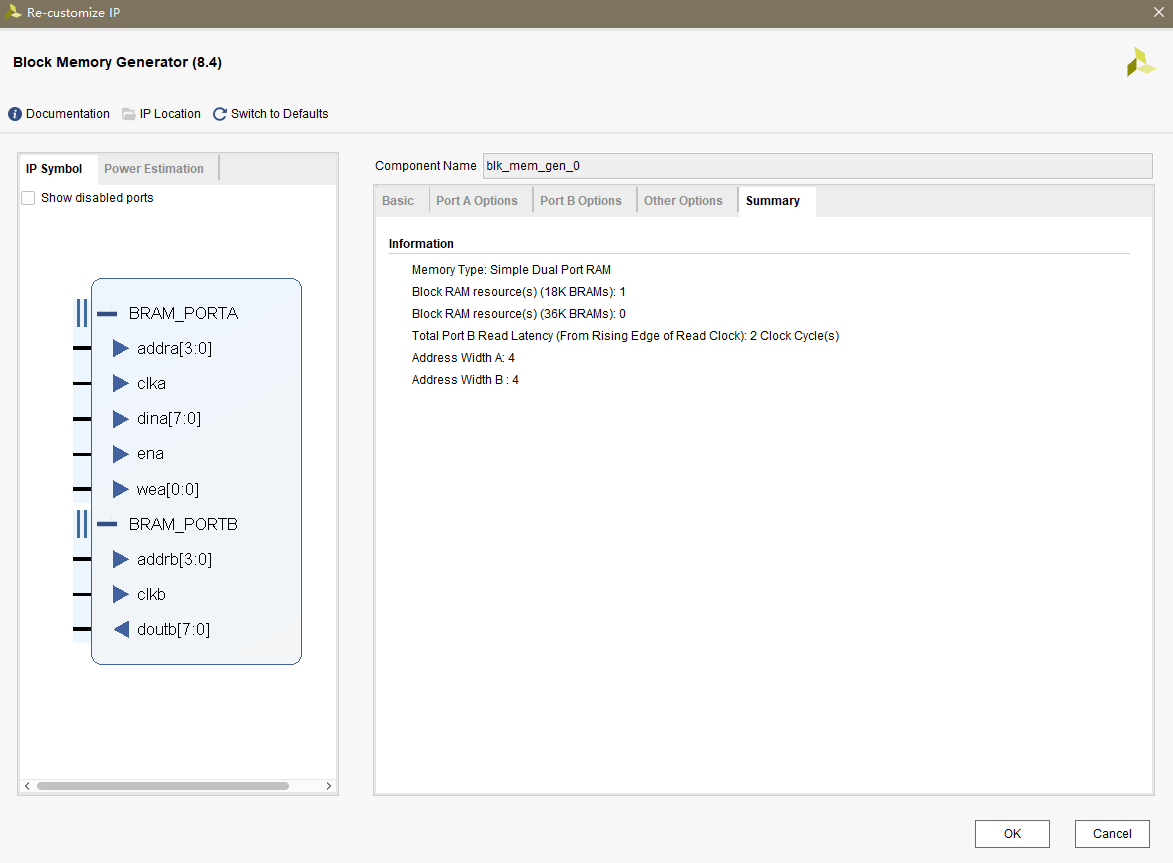

IP 核配置

测试及仿真:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/10/26 16:34:06

// Design Name:

// Module Name: testbench

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module testbench #(

parameter DATASIZE = , //Memory data word width

parameter ADDRSIZE = ) //Number of mem address bits depth = 16 ( input wire clk,

input wire rst, output [DATASIZE- : ] rdata ); //------------------------------------------------------------ reg [:] i = ;

reg [DATASIZE- : ] wdata = ;

reg [ADDRSIZE- : ] waddr = ;

reg wclken = ;

reg [ADDRSIZE- : ] raddr = ;

always @(posedge clk or posedge rst)

begin

if(rst)

begin

i <= ;

wdata <= ;

waddr <= ;

wclken <= 'b0;

raddr <= ;

end

else

begin

case(i)

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b1;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b0;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i + ;

wclken <= 'b0;

raddr <= ;

end

:

begin

wdata <= ;

waddr <= ;

i <= i ;

wclken <= 'b0;

raddr <= ;

end endcase

end

end //------------------------------------------------------------ wire wfull ;

assign wfull = ; //------------------------------------------------------------ wire [DATASIZE- : ] rdata; fifomem #(

.DATASIZE (), //Memory data word width

.ADDRSIZE ()) //Number of mem address bits depth = 16

U0 (

.wdata(wdata),

.waddr(waddr),

.wclken(wclken),

.wfull(wfull),

.wclk(clk),

.raddr(raddr),

.rdata(rdata)

); endmodule /* add_force {/testbench/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/testbench/rst} -radix hex {1 0ns} {0 200ns} */

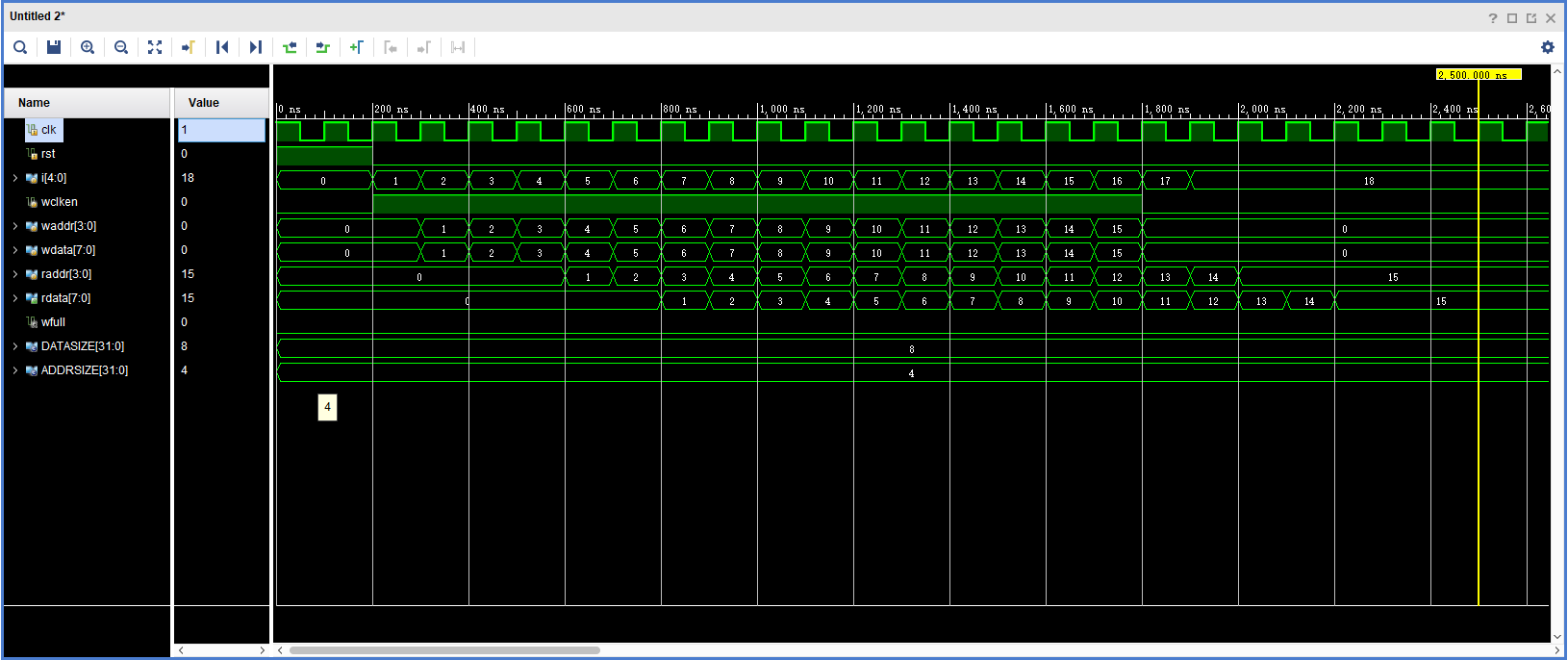

仿真波形图:

从RAM读出来的数据会比给定的地址晚两拍。

使用仿顺序操作来写testbench也是极好的。

最新文章

- C#进阶系列——WebApi 异常处理解决方案

- *HDU 1709 母函数

- JavaScript测试工具比较: QUnit, Jasmine, and Mocha

- 足球游戏AI_资料收集

- sina sae 部署 java ssh 项目

- java 开发, jdk 1.6 官方下载地址

- class对象不太明白(待解答)

- C#代码分层的好处

- git 之别名配置

- kubernetes云平台管理实战: pod资源共享(三)

- Hadoop Mapreduce运行流程

- 洛谷P3178 [HAOI2015]树上操作

- User-Defined Variables

- 杭电hdu-6168 Numbers

- 除虫记之C#调用C函数出现的诡异错误

- IIS错误提示:另一个程序正在使用此文件 进程无法访问

- 680C. Bear and Prime 100 数学

- C# 使用log4net写日记

- python独立环境——virtualenv

- unity, Find References In Scene