create_generated_clock 的用法

本文转载自:create_generated_clock_亓磊的博客-CSDN博客_create_generated_clock

文章目录

参数source和master_clock区别

source是时钟源的pin,工具会根据source pin找到master时钟,generated时钟相位是基于source pin描述的。

master_clock是时钟源的时钟名称,而且要伴随参数-add,表明一个master_clock,有多个source pin路径。

create_clock叫master时钟;

create_generated_clock叫generated时钟。

总之,create_generated_clock 是用来说明generated clock与source pin的相位(边沿)关系。同时 根据source pin 找到master clock以及source pin 和master clock的关系, 最终会确定generated clock和master clock的相位(边沿)关系。

create_generated_clock 介绍

create_generated_clock 是用来说明generated clock与source clock的相位(边沿)关系,

同时根据source clock找到master clock以及source clock 和master clock的关系,

最终会确定generated clock和master clock的相位(边沿)关系。

相对create_clock的区别,是继承了master_clock的相位特性。

在genereated clock的时候一定要明确generated clock与master clock的相位关系(rise->rise or rise->fall or fall->rise or fall->fall),

这些关系由桥梁source clock嫁接,所以需要名曲generated clock和source clock,以及source clock和master clock的关系,如果根据声明找到的generated clock

和master clock的关系和实际的关系不一致,否则会造成一些分析错误。

如:sta的时候找不到generated clock和source clock相位关系,会将generated clock的source latency 设置为0

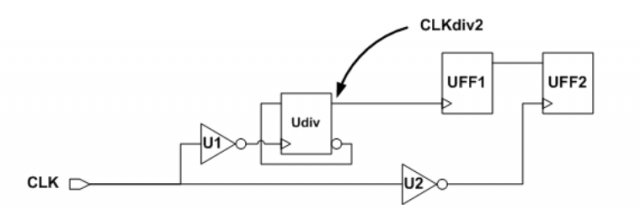

如下图:

举例:注意:CLKdiv2的source,应为~CLK,CLK的反相。

create_clock -period 10 CLK

create_generated_clock \

-name CLKdiv2 \

-divide_by 2 \

-source CLK \

[get_pins Udiv/Q]

这个例子,会导致CLKdiv2和CLK的相位有180°的相位差,这个约束与设计是不符合的。这个例子是有问题的。

根据声明,generated 和master clock的关系如下(工具会根据source clock 找到master clock,并确定source clock 和master clock的关系,当前source clock即master clock)。

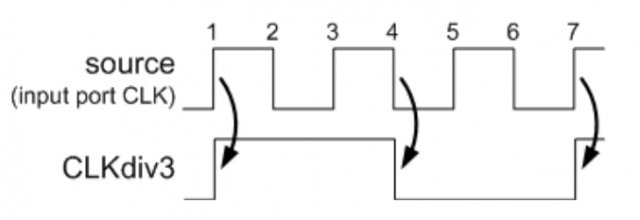

下图:(原作者画成了3分频,不过原理一样,就不改了。)

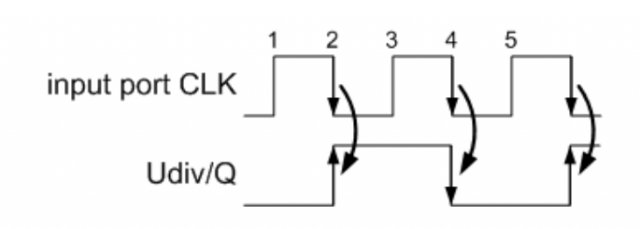

而实际上的,generated 和 master clock的关系如下

解决方法有2种:

1.改变generated clock的source,即让generated clock和source clock的路径唯一且单一(单一是指,声明的相位边沿关系和实际的相位边沿关系一致)。

一般做法就是将source clock设置在触发器的clock端。如下:

create_generated_clock \

-name CLKdiv2 \

-divide_by 2 \

-source [get_pins Udiv/CLK] \

[get_pins Udiv/Q]

这样generated clock和source clock的关系和声明的一致。

工具会根据声明的source clock 找到它的master clock,同时确定source clock和master clock相位相反的关系,

由此就确定了generated clock和master clock的关系。

2.直接声明generated clock和master clock的相位边沿关系。如下:

create_generated_clock \

-name CLKdiv2 \

-edges {2 4 6}

-source CLK \

[get_pins Udiv/Q]

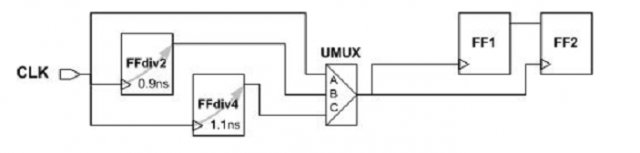

create_generated_clock有多个master_clock的情况

这个情况,需要特别处理。

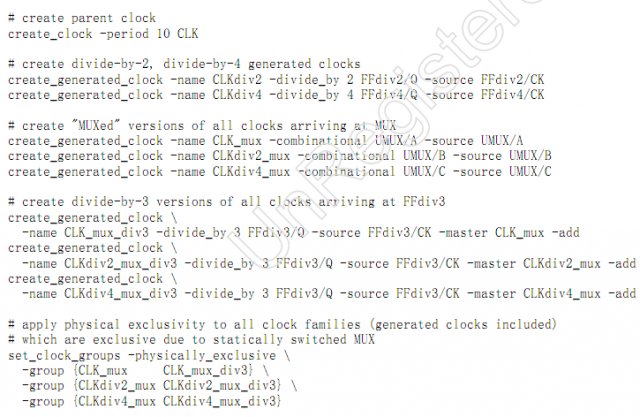

create_clock -period 10 CLK

create_generated_clock \

-name CLKdiv2 \

-divide_by 2 \

-source FFdiv2/CLK \

UMUX/Y \

-master CLK -add

create_generated_clock \

-name CLKdiv4 \

-divide_by 4 \

-source FFdiv4/CLK \

UMUX/Y \

-master CLK -add

set_clock_groups -physically_exclusive \

-group {CLK} \

-group {CLKdiv2} \

-group {CLKdiv4}

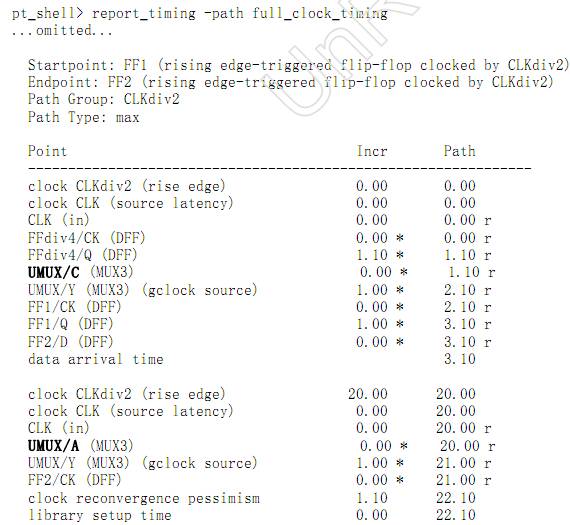

此时,PT时序分析报告如下:

可以知道source latency 选择了不同路径

所以在声明generated clock的时候不仅要保证generated clock 和master clock 相位边沿关系和实际的一致,还要保证generated clock和master clock的路径唯一。

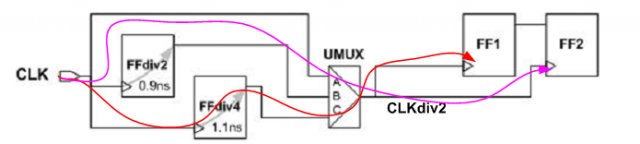

如下图,列出了可以声明唯一generated clock点。

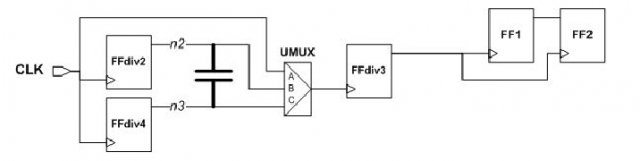

同时考虑到选择器之前各个时钟间有crosstalk,选择器之后没有crosstalk,所以声明如下:

总而言之,create generated clock的时候要保证2点

1.一致性:声明的generated clock和master clock相位边沿的关系要和实际的一致。

2.唯一性:确保generated clock和master clock的路径的唯一。

满足上面2点,在STA分析的时候就不会造成不必要的误解。

若直接将 CLKmux, clkdiv2_mux, clkdiv4_mux 省略,然后分别在MUX/Y端定义三个generated clock,其 source 设定为CLK, CLKdiv2, CLKdiv4,也是可以的。

最新文章

- canvas中的rotate的使用方法

- 基于php开发的RESTful ApiDoc文档

- js错误:TypeError $(...) is null

- 硅谷新闻4--解决页签手指按下从左到右滑动的bug

- Spring读取配置文件的几种方式

- mplayer-for-windows change color scheme in win 7

- 一步步学习ASP.NET MVC3 (11)——@Ajax,JavaScriptResult(2)

- HDU 3127 WHUgirls(DP 完全背包)

- 版本控制工具git入门

- filter过滤器执行顺序

- Redis实现分布式锁与任务队列

- C语言多维数组的指针传递

- sklearn交叉验证2-【老鱼学sklearn】

- 尝试了一些时间,最简单的apache上设置用IP访问一个虚拟目录

- 【cocos2d-x 手游研发小技巧(2)循环无限滚动的登陆背景】

- 小刘的深度学习---Faster RCNN

- WebApi参数问题方案

- 38.Count and Say 报数

- ps裁剪一寸照片及换背景色

- AsyncTask doinbackground onProgressUpdate onCancelled onPostExecute的基本使用