Verilog-case、casez和casex的区别

2024-09-06 17:33:20

参考博客:https://www.cnblogs.com/guolongnv/articles/6906929.html

1、基本概念

1)?表示z,而不是“dont care”

2)区分:

case语句的表达式的值有4中情况:0、1、z、x。4种是不同的,故表达式要严格的相等才可以操作分支语句。

casez语句中的表达式情况有三种:0、1、x。不用关心z,z可以和任何数值相等,即z =0.z= 1,z=x;

casex语句的表达式情况有二种:0、1.不用关心x和z。即x=z=0,x=z=1.

2、测试代码

`timescale 1ns / 1ps

module case_compare(

input[:] sel,

output reg [:] y, input[:] z_sel,

output reg [:] z_y, input[:] x_sel,

output reg [:] x_y ); always @(*) begin

case(sel)

'b00: y = 2'b00;

'b01: y = 2'b01;

'b1?: y = 2'b10;

default: y = 'b11;

endcase

end always @(*) begin

casez(z_sel)

'b00: z_y = 2'b00;

'b01: z_y = 2'b01;

'b1?: z_y = 2'b10;

default: z_y = 'b11;

endcase

end always @(*) begin

casex(x_sel)

'b00: x_y = 2'b00;

'b01: x_y = 2'b01;

'b1?: x_y = 2'b10;

default: x_y = 'b11;

endcase

end endmodule

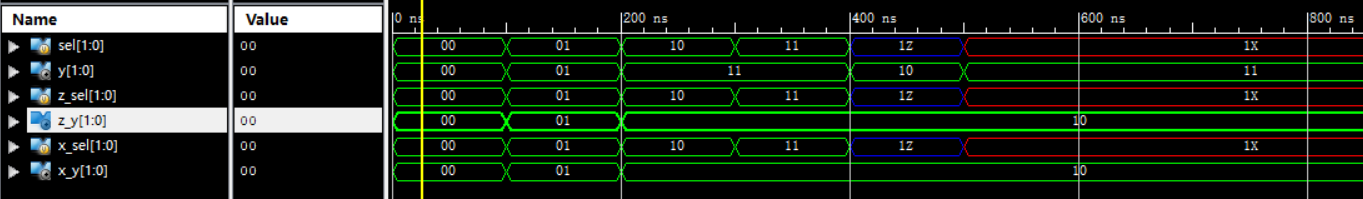

1)前仿真波形

2)综合后仿真波形

对比波形可以看出来,case(不是casez/casex的时候)的index列表里面的x和z,都被综合工具认为是不可达到的状态就被去掉了。

casez和casex里面的x/z都被认为是don't care,所以综合出的电路会是一致的。

3、使用建议

1)我们在写代码的时候如果用了case,那么就不要在index列表里面出现x/z/?,综合工具认不出这些,都会当做don't care

2)casez和casex综合的结果是一致的。

3)casez稍好用一些,因为它可以用来代表don't care的值

4)最重要的一点就是,casez和casex其实没有孰优孰劣

最新文章

- NK3C:关于svg文件使用

- 项目:DoubleFaceCamera

- 获取 .net framework 路径

- HDU2222 Keywords Search(AC自动机模板)

- 九度OJ 1534 数组中第K小的数字 -- 二分查找

- java之NIO编程

- 文成小盆友python-num15 - JavaScript基础

- CSS中文字体的英文名称 – 前台开发必备

- VirtualBox 安装 Ubuntu 14.04 无法调节分辨率问题

- VNC 分辨率修改

- c++入门之——const在函数名前面和函数后面的区别

- 【gearman】gearmand -d 无反应解决

- phpMyadmin安装极简教程[下载,解压,登录]

- spring配置上传文件大小

- R中ifelse、which、%in%的用法

- IOS控制系统手势返回

- U盘安装OSX

- Android——保存和恢复用户状态

- Ubuntu解压命令全览

- DP Intro - poj 1947 Rebuilding Roads(树形DP)