使用verilog编写锁存器与触发器

需要注意的地方有四点:

1、关于锁存器与触发器在原理上的不同点,以及代码的不同点

2、关于高电平有效与低电平有效之前的区别

3、理解实现复位与实现D触发器之间的区别

4、理解同步与异步之间的区别

锁存器代码编写

|

Module D_latch(d,clk,q); Input d; Input lck; Output reg q; always@(clk or d) if(clk) q<=d; endmodule |

D触发器,标准

|

Module D_ff(d,clk,q); Input d; Input lck; Output reg q; always@( posedge clk) q<=d; endmodule |

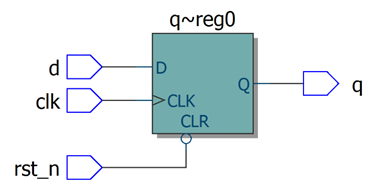

异步低有效D触发器

注意高电平有效跟低电平有效之间的区别

|

module code(clk,rst_n,d,q); input clk; input rst_n; input d; output reg q; always @( posedge clk or negedge rst_n) begin if(!rst_n) q <= 1'b0; else q <= d; end endmodule |

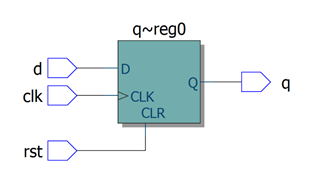

异步高有效D触发器

|

module code(clk,rst,d,q); //关于高有效还是低有效,都是驱动clk对输出端进行使能,有效 即为输 出为0,并不是输出要等于复位信号的值。 input clk; input rst; input d; output reg q; always @( posedge clk or posedge rst ) //注意这里是两个上升沿,高电平有效 begin if(rst) q <= 1'b0; else q <= d; end endmodule |

同步高有效D触发器

也就是说同步复位触发器时,必须使用触发器之外的门逻辑,才能构成同步触发器。

|

module code(clk,rst,d,q); input clk; input rst; input d; output reg q; always @( posedge clk) begin if(rst) q <= 1'b0; else q <= d; end endmodule |

最新文章

- Java代理模式/静态代理/动态代理

- Ubuntu16.04下安装.NET Core

- ACM: Mr. Kitayuta's Colorful Graph-并查集-解题报

- STL中的map/multimap小结

- iOS开发网络篇—网络请求(HTTP协议)小结(转)

- MySQL Replication的相关文件

- xml学习总结(四)

- Paginator

- mysql locktables

- 非常不错 Hadoop 的HDFS (Hadoop集群(第8期)_HDFS初探之旅)

- HTML5表单提示placeholder属性兼容IE

- Cake

- <marquee>,视频和音频的插入,正则表达式

- Android系统--Binder系统具体框架分析(二)Binder驱动情景分析

- 【代码学习】MYSQL数据库的常见操作

- git命令记录

- OpenCV提取显示一张图片(或者视频)的R,G,B颜色分量

- 20165214 2018-2019-2 《网络对抗技术》Exp4 恶意代码分析 Week6

- RoR- Database setup& SQLite ... Migrations

- nyoj-0708-ones(dp)