DDR3(4):读控制

2024-09-04 07:29:28

写控制完成后开始设计读控制,写控制和读控制是非常相似的。

一、总线详解

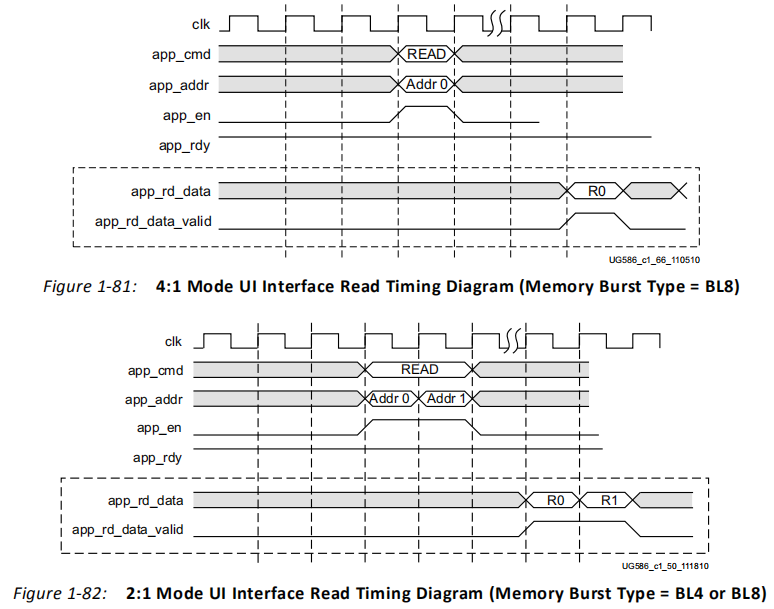

由 User Guide 可知各信号之间的逻辑关系,读数据是在给出命令之后一段时间后开始出现的。图中没有给出app_rd_data_end信号,此信号和app_wdf_end是相同的,即在DDR3的物理层端与用户端存在两种速率情况,此次设计速率为4:1,app_rd_data_end 和 app_rd_data_valid 相同。

二、读控制模块设计

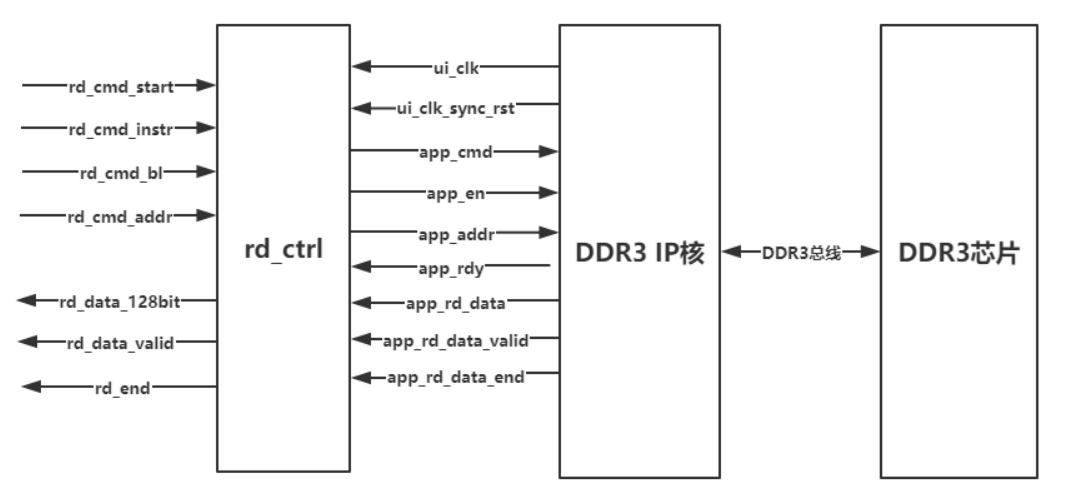

本次设计读控制模块,试着将之前写控制模块的64个128bit数据读回来,并最终进行仿真验证。写控制模块框图如下所示:

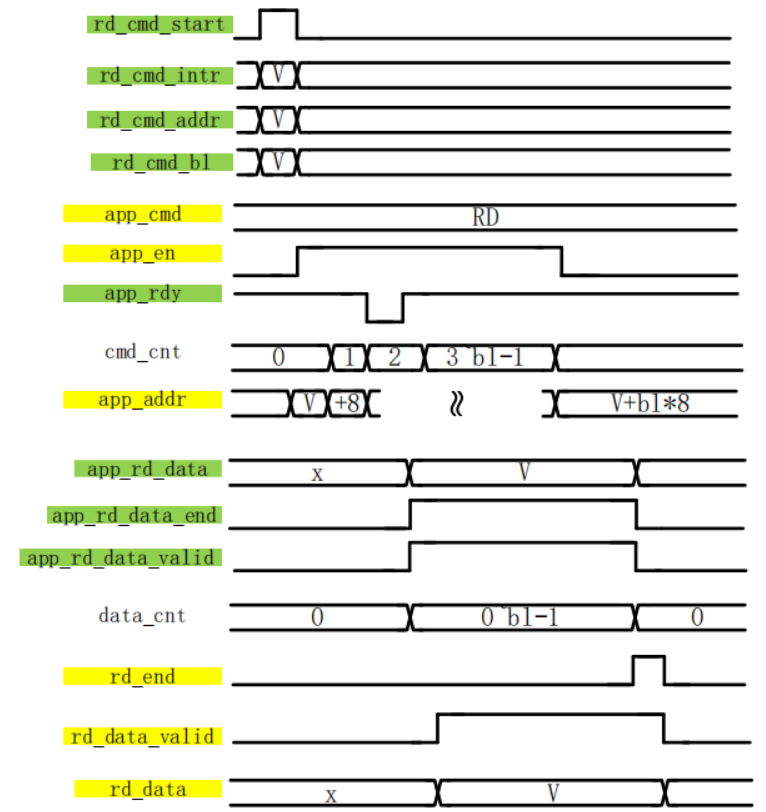

当 rd_cmd_start 有效时,启动本次的读突发,根据由外部输入的 rd_cmd_bl 可以确定本次突发需要读多少个数据。wr_cmd_addr 代表本次突发读的起始地址,数据是128bit的,一个地址能存16bit,因此每个128bit数据需要占用8个地址,即每次的地址计数+8。rd_end 用于告知其他模块,本次突发读结束。

本次设计均学自《威三学院FPGA教程》,具体代码就不贴了。

顶层文件不要忘了例化此模块,此外此处设计只考虑读控制,应该把top层中写控制先注释掉,以免两方打架。关于如何复用总线,见下一章:仲裁模块

/*

//写控制模块 ---------------------------------------------------------------

wr_ctrl u_wr_ctrl

(

.sclk (ui_clk ), // input 100Mhz

.rst (ui_clk_sync_rst | (~init_calib_complete)), // input

.wr_cmd_start (wr_cmd_start ), // input

.wr_cmd_instr (wr_cmd_instr ), // input [ 2:0]

.wr_cmd_bl (wr_cmd_bl ), // input [ 6:0]

.wr_cmd_addr (wr_cmd_addr ), // input [27:0]

.wr_cmd_mask (wr_cmd_mask ), // input [15:0]

.data_128bit (data_128bit ), // input [127:0]

.data_req (data_req ), // output

.wr_end (wr_end ), // output

.app_rdy (app_rdy ), // input

.app_wdf_rdy (app_wdf_rdy ), // input

.app_en (app_wr_en ), // output

.app_addr (app_wr_addr ), // output [27:0]

.app_cmd (app_wr_cmd ), // output [ 2:0]

.app_wdf_mask (app_wdf_mask ), // output

.app_wdf_wren (app_wdf_wren ), // output

.app_wdf_data (app_wdf_data ), // output [127:0]

.app_wdf_end (app_wdf_end ) // output

);

*/ //读控制模块 ----------------------------------------------------------------

rd_ctrl u_rd_ctrl

(

.sclk (ui_clk ), // input 100Mhz

.rst (ui_clk_sync_rst | (~init_calib_complete)), // input

.rd_cmd_start (rd_cmd_start ), // input

.rd_cmd_instr (rd_cmd_instr ), // input [ 2:0]

.rd_cmd_bl (rd_cmd_bl ), // input [ 6:0]

.rd_cmd_addr (rd_cmd_addr ), // input [27:0]

.rd_data_128bit (rd_data_128bit ), // output [127:0]

.rd_data_valid (rd_data_valid ), // output

.rd_end (rd_end ), // output

.app_rdy (app_rdy ), // input

.app_en (app_rd_en ), // output

.app_addr (app_rd_addr ), // output [27:0]

.app_cmd (app_rd_cmd ), // output

.app_rd_data (app_rd_data ), // input

.app_rd_data_valid (app_rd_data_valid ), // input

.app_rd_data_end (app_rd_data_end ) // input

);

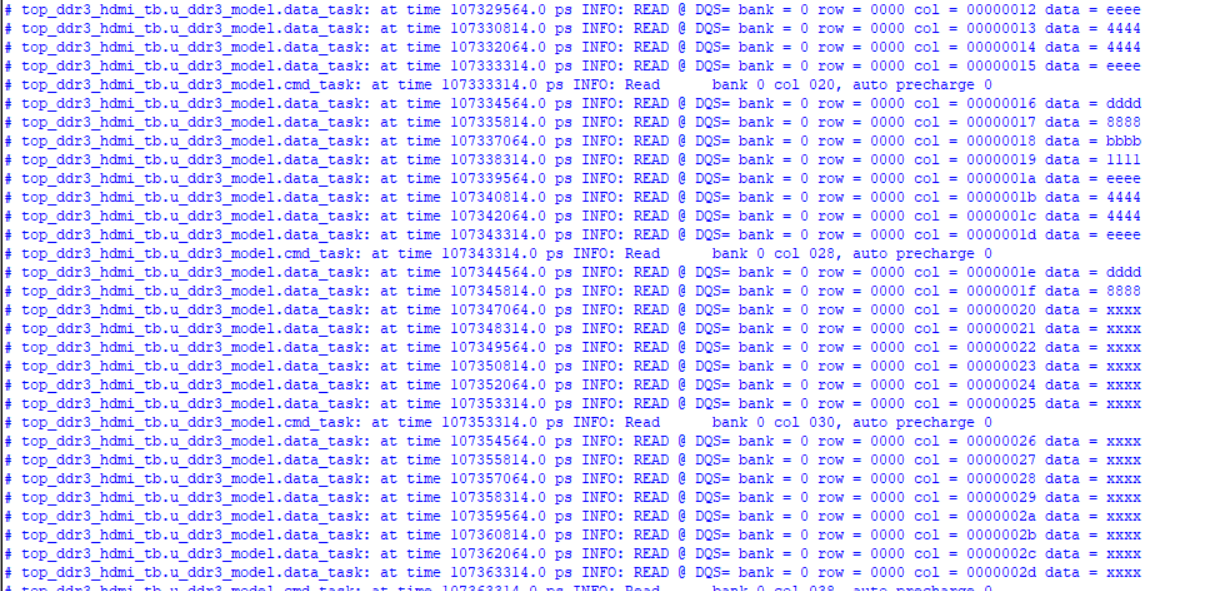

三、读控制模块仿真

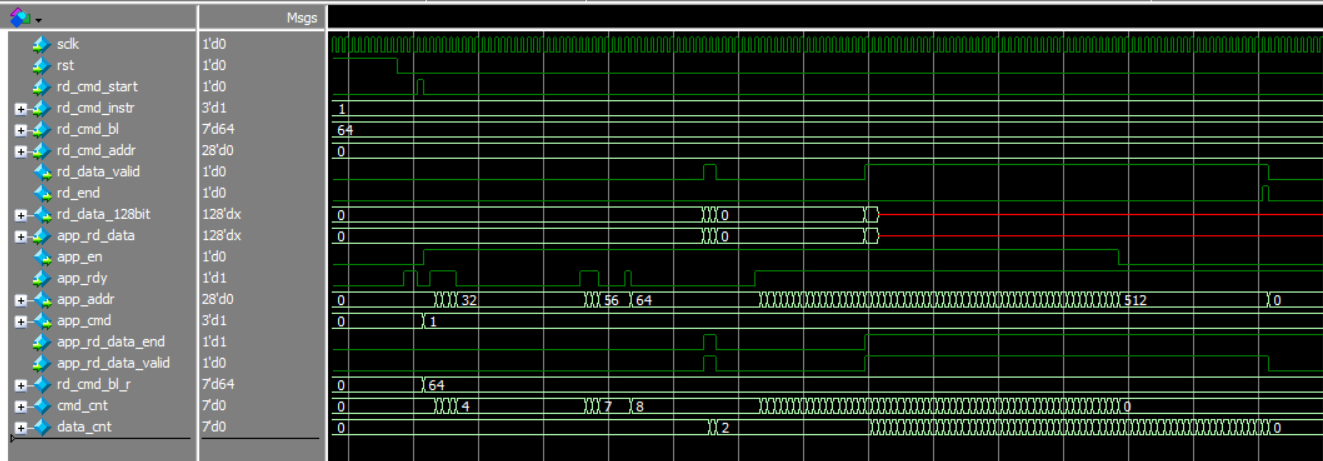

可以看到一开始读出的数据是ddr3进行自我校验时残留的数据,后面则都是xxxx,由此看出读控制模块设计大致成功,具体对不对得结合写控制,那就涉及到信号复用了,下章记录仲裁模块解决读写复用问题。

参考资料:威三学院FPGA教程

最新文章

- Windows Azure Service Bus Notification Hub推送通知

- Android自定义View滑动事件处理总结

- eBay 消息发送(1)

- C#借助谷歌翻译实现翻译小工具(二)添加托盘图标

- axure变量的使用

- I - Control - HDU 4289 (最大流)

- [wikioi]数的划分

- fdisk -l 找不到分区怎么办?想办法找到隐藏分区。

- Counting square

- Memcached缓存系统介绍及安装

- LaTeX排版指南

- 模拟教室网络(跨VLAN,跨网段通讯)

- gstreamer在Ubuntu下构建开发环境

- IDEA中debug启动tomcat报错。Error running t8:Unable to open debugger port(127.0.0.1:49225):java.net.BindException"Address alread in use:JVM_Bind"

- IE上如何设置input type=file的光标不闪烁

- Mybatis配置返回为修改影响条数

- 「BZOJ」「3262」陌上花开

- MVC + ajaxform 文件上传

- 【链表】Sort List(归并排序)

- es6 中的generator函数控制流程