【实战经验】--Xilinx--IPcore--PLL生成

用途:

PLL用于产生自己想要的时钟,可以倍频有可以分频,通常倍频。

生成:

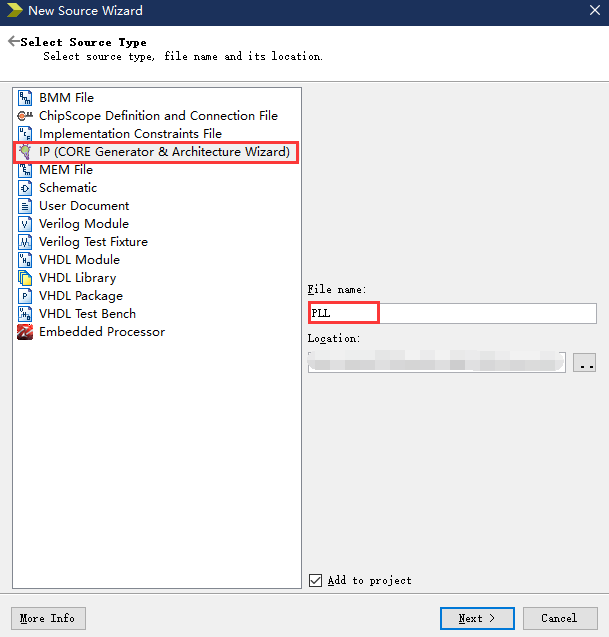

1.打开ISE—— Project —— New source,选择IP(CORE Generator & Architecture Wizard),再命名你要产生的IP核,点击Next

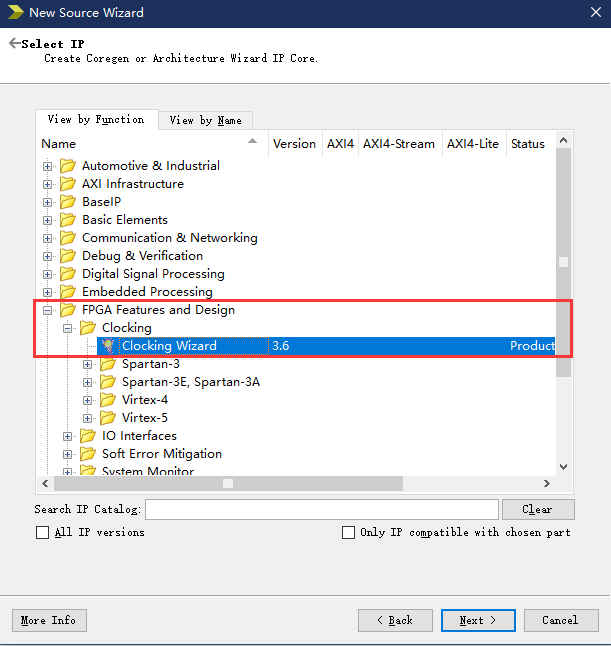

2.选择FPGA —— Features and Design —— Clocking —— Cloking Wizard 点击Next

3.选择Finish(未配图)进入配置界面。

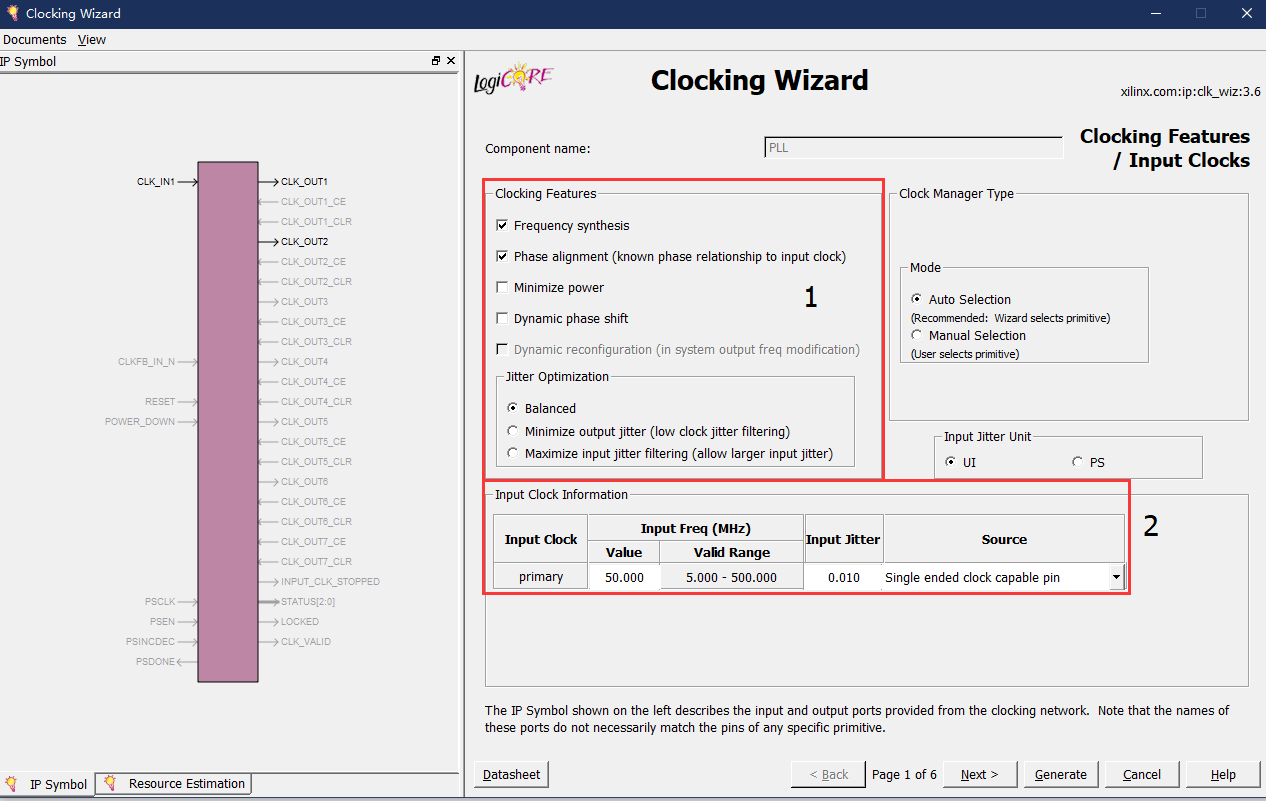

这里主要说两点(如上图)

3.1Cloking Features

Frequency synthesis 允许输出多个输入时钟不同的时钟,通常选择,不选择的话 输出时钟=输入时钟。

Phase alignment 此功能允许将输出时钟相位锁定到参考,例如设备的输入时钟针。

Minimize power 该特征可以使原语需要的功率总量最小化,但可能是以频率、相移、以及占空比精度为代价的。通常不选择。

Dynamic phase shift 此功能允许更改输出时钟上的相位关系

3.2 Input Clock Information

Value 输入时钟频率(我的板子上是50MHz)

Input Jitter 输入抖动(默认即可)

Source 下拉有四个选项:第一个选择的意思是输入时钟为单端的,有一个IBUFG作为输入时钟缓冲;

第二个为差分输入端,一个IBUFGDS被嵌入主输入时钟中;

第三个为全局缓冲,一个BUFG被嵌入主输入时钟中;

第四个就是没有buffer。

配置好后点击NEXT进入下一个配置界面。

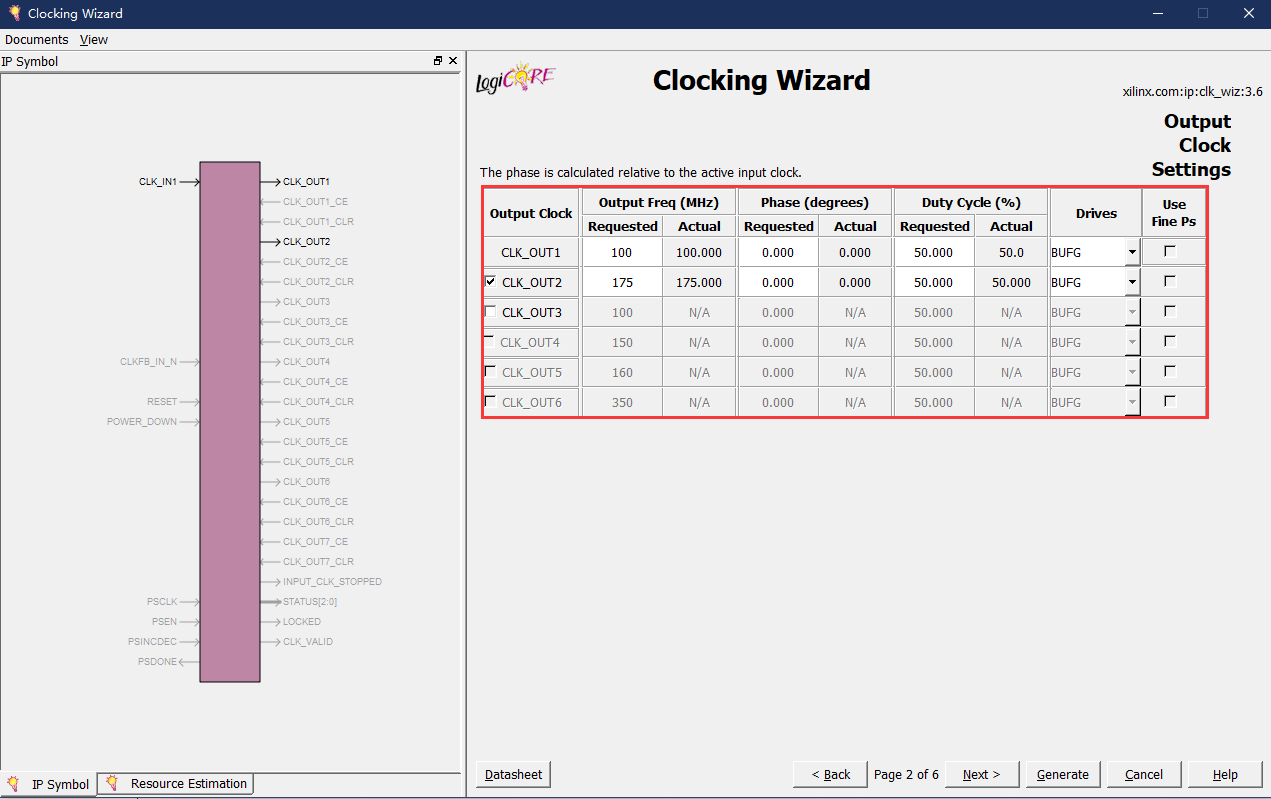

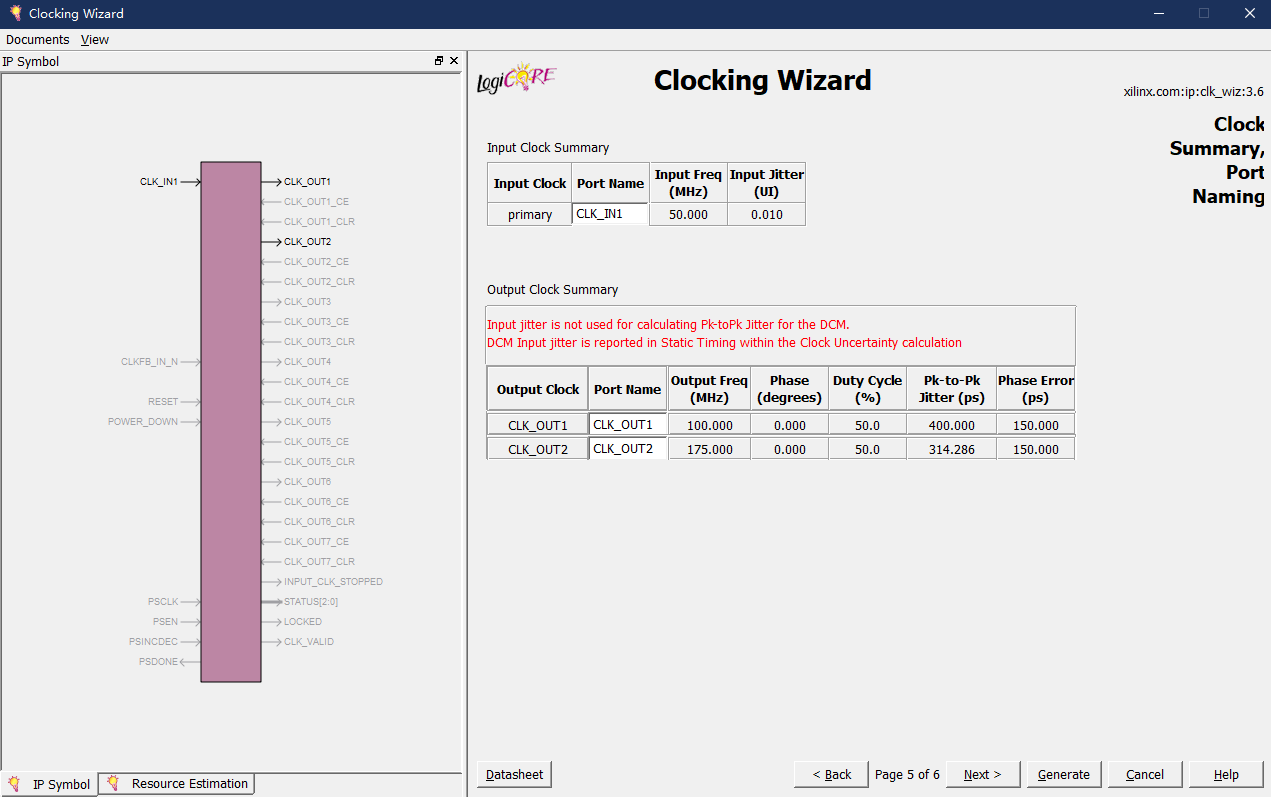

5.这个界面设置输出时钟的个数(Output Clock)、频率(Output Freq)、相位(Phase)、占空比(Duty Cycle),设置好后点击NEXT

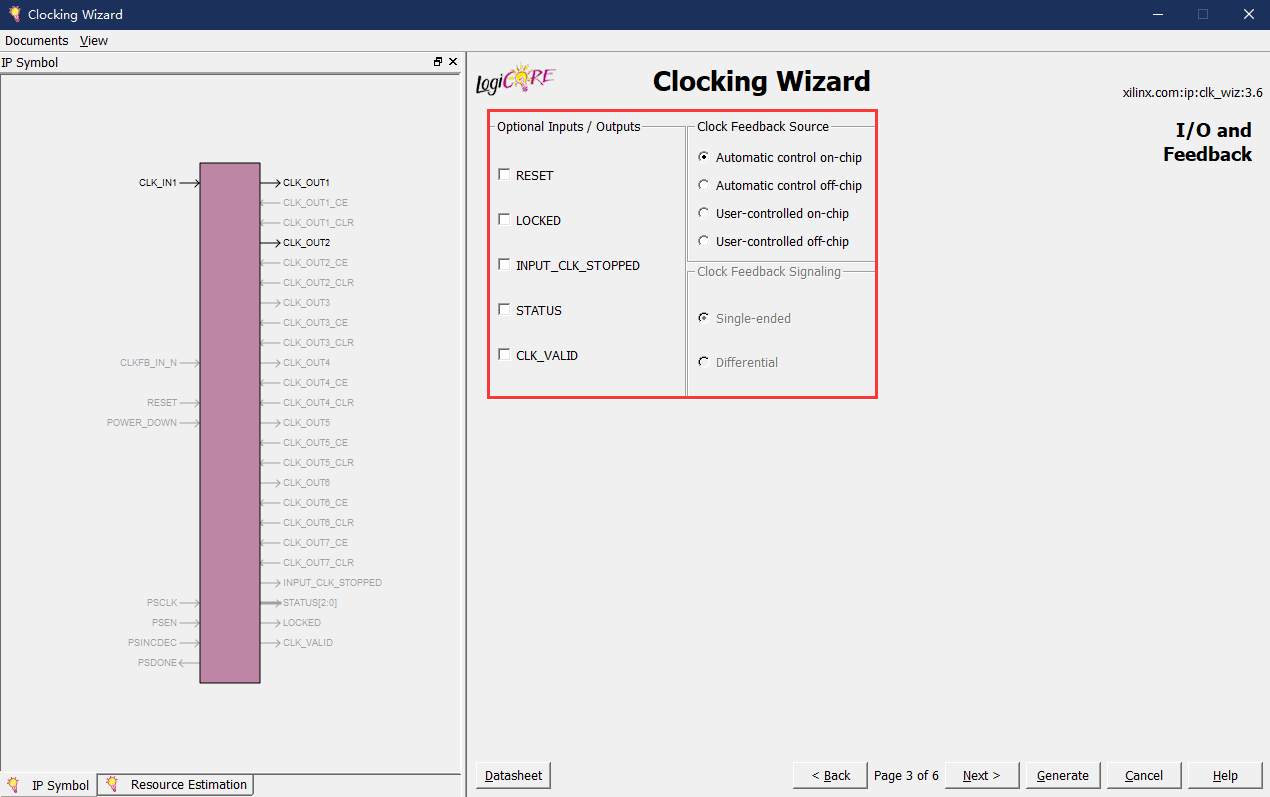

5.这里配置一些其他的信号

RESET 复位PLL(高电平有效)

LOCKED PLL输出时钟正常工作的指示信号

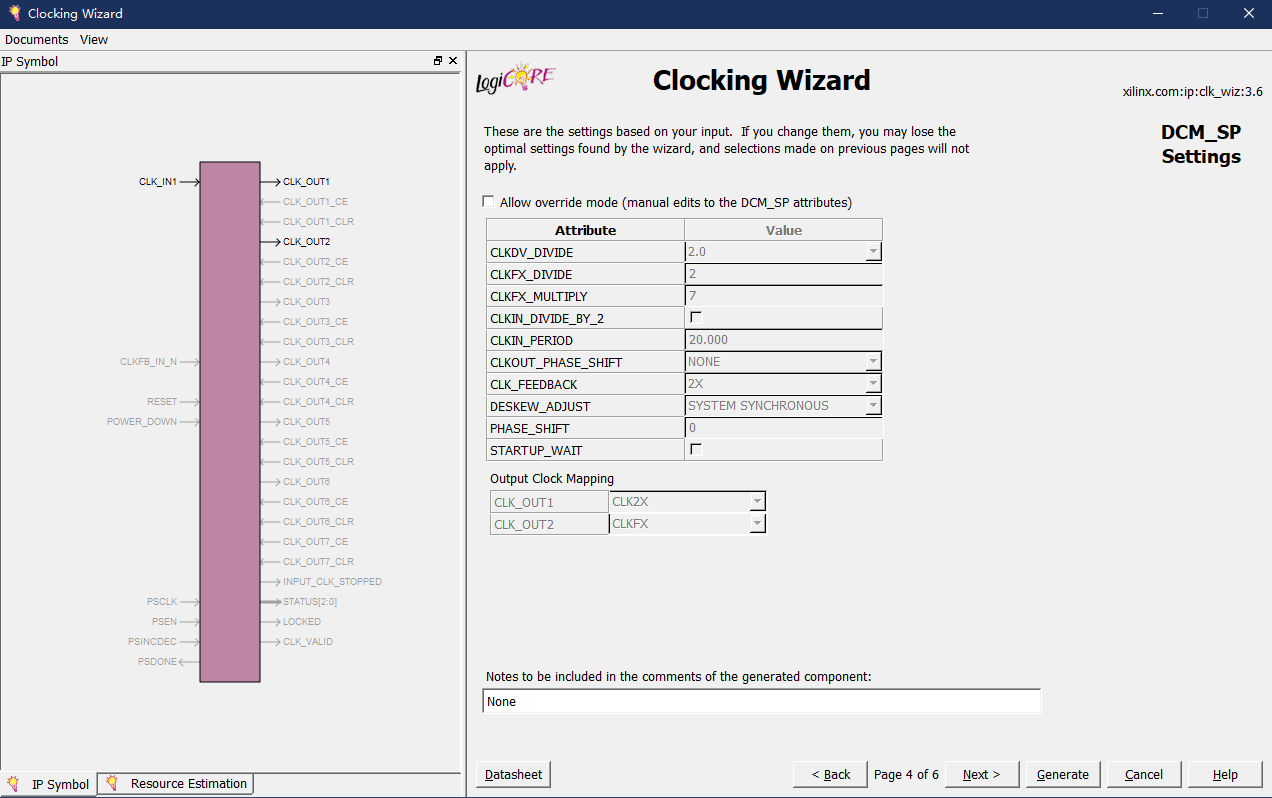

6.最好别修改这里的数值,直接点击NEXT

7.改输入输出时钟的名字,不改可以直接点击NEXT

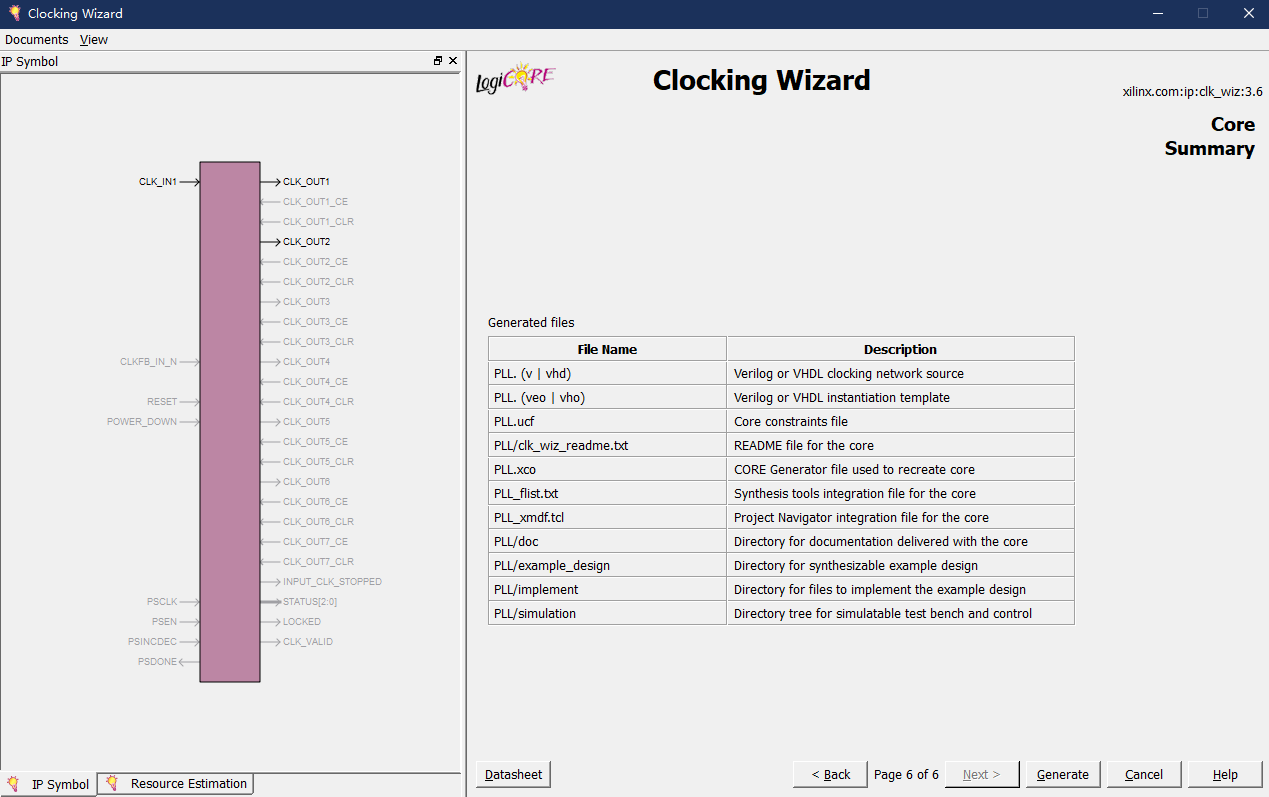

8.点击Generate即可生成一个PLL IPcore

例化:

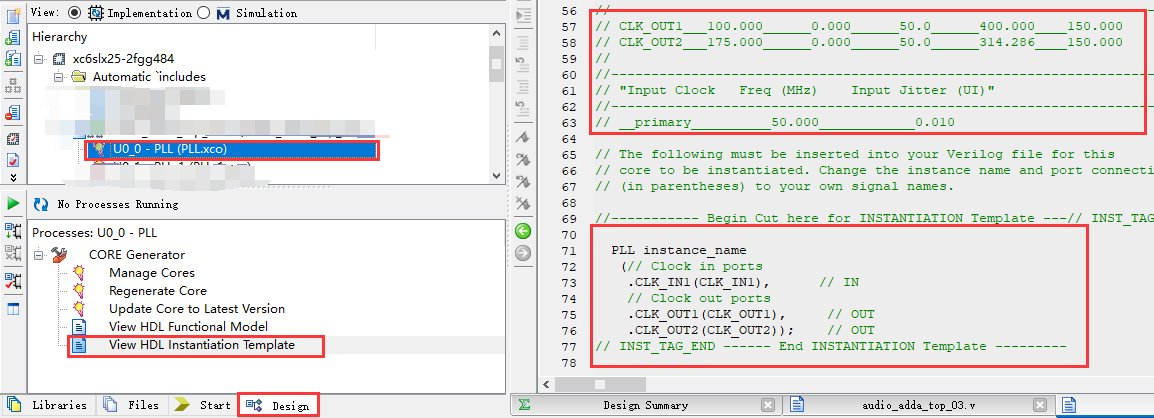

Design栏单击生成的IP核,再在下方的CORE Generator中双击View HDL INstantiation Template,即可在右侧查看信息(上)及例化模板(下),复制例化模板在其他地方粘贴并修改即可。

最新文章

- 速战速决 (1) - PHP: 概述, 常量, 变量, 运算符, 表达式, 控制语句

- android switch(String)错误:Cannot switch on a value of type String for source level below 1.7

- 【leetcode】 search Insert Position(middle)

- Hibernate条件查询

- android开发 两张bitmap图片合成一张图片

- centos7搭建NIS与NFS综合应用

- CSS——选择器

- 解开Android应用程序组件Activity的"singleTask"之谜

- ExperDot的博客目录导航

- 手动编译protobuf3的C++源码

- Spring Boot 文件上传

- IBM SPSS 实习总结

- springmvc定时任务

- C-fopen,fwrite,fread,fseek,fgets,popen,access笔记

- OCM_第十七天课程:Section7 —》GI 及 ASM 安装配置 _管理和配置 GRID /实施 ASM 故障组 /创建 ACFS 文件系统

- 《C#本质论(第4版)》

- 字符串hash&&对字符串hash的理解

- 【微信开发】PC端 微信扫码支付成功之后自动跳转

- Easyui Datagrid相同连续列合并扩展(二)

- 引用数据数据类型Scanner、Random