FPGA 状态机-序列检测器verilog

2024-08-29 23:26:16

实现功能:检测出串行输入数据4位Data二进制序列0101,当检测到该序列的时候,out=1,否则out=0

(1)给出状态编码,画出状态图

(2)门电路实现

(3)verilog实现

首先规定Q3Q2Q1为刚输入的三位数,接下来要输入的数是A,Z为输入A以后的状态机的输出结果,则可以画出状态转换图如下:

然后根据状态图,我们可以得到状态表:

从而推导出激励方程,根据卡诺图化简得到序列检测的门级检测电路如下:

(3)根据状态图写出verilog代码:

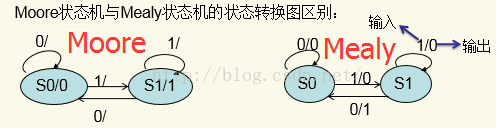

mealy型状态机的输出与其输入以及当前状态有关:

module xuliejiance(input clk,rst,q

output out);

reg [:]state,nexts;

parameter s1='d0,

s2='d1,s3=3'd2,s4='d3,s5=3'd4,

s6='d5,s7=3'd6,s8='d7; always@(posedge clk ir negedge rst)

begin

if(~rst)

state<='d0;

else

state<=nextstate;

end always@(q,state)

case(state)

:if(q==)

nextstate='d1;

else

nextstate='d0;

:if(q==)

nextstate='d3;

else

nextstate='d2;

:if(q==)

nextstate='d5;

else

nextstate='d4;

:if(q==)

nextstate='d5;

else

nextstate='d6;

:if(q==)

nextstate='d0;

else

nextstate='d1;

:if(q==)

nextstate='d0;

else

nextstate='d3;

:if(q==)

nextstate='d0;

else

nextstate='d4;

:if(q==)

nextstate='d7;

else

nextstate='d6;

default:

nextstate<='d0;

endcase

assign out=(state==3'd2)&&(x==0);

endmodule

moore型状态机的输出只与其当前状态有关:

module xuliejiance(

input clk,rst,q,

output out);

reg [:] state,nextstate;

parameter s0='d0,s1=3'd1,s2='d2,s3=3'd3,s4='d4;

always @(posedge clk or negedge rst)

begin

if(~rst)

state<='d0;

else

state<=nextstate;

end always@(*)

begin

case(state)

s0:

begin

if(q==)

nextstate=s1;

else

nextstate=s0;

end

s1:

begin

if(q==)

nextstate=s2;

else

nextstate=s0;

end

s2:

begin

if(q==)

nextstate=s2;

else

nextstate=s3;

end

s3:

begin

if(q==)

nextstate=s4;

else

nextstate=s0;

end

s4:

begin

if(q==)

nextstate=s0;

else

nextstate=s1;

end end

assign out=(state==s4)?1:0;

endmodule

以上写的都是两段式的状态机的实现,此外我们可以用更加正式的三段式的状态机实现

以下是一个可以用与参考的状态机的东西:

我们以1101序列检测器为例:

1101序列检测器Mealy状态机状态转移图

1101序列检测器Moore状态机状态转移图

我们以Mealy状态机为例

一段式状态机(部分核心代码):

两段式状态机(部分核心代码):

三段式状态机(部分核心代码):

最新文章

- 让你的站点也支持MarkDown

- JS函数输出圆的半径和面积

- mysql.my.cnf

- js获取url地址中的参数

- 面向对象编程语言中的接口(Interface)

- Android shape 渐变!描边!圆角!示例详解

- 【PRML读书笔记-Chapter1-Introduction】1.2 Probability Theory

- Dinic 算法

- D3.js 布局

- 【转】Linux设备驱动之Ioctl控制

- 用VMware 8安装Ubuntu 12.04详细过程(图解)

- cocos2d-x图片变灰或者变亮

- 集群搭建必备:虚拟机之一实现Host-only方式上网

- Fedora 18 安装前指南

- 20.如何从app业务逻辑提炼api接口

- day05 模块学习

- 聚合函数与F/Q表达式

- dubbo白名单通过filter,spring web通过拦截器或者filter即可

- Pandas 删除指定列中为NaN的行

- JSP笔记03——环境搭建(转)