DDR3(3):写控制

调取的 DDR3 控制器给用户端预留了接口,用于实现对该 IP 核的控制,本篇介绍一下 DDR3 IP核写。在生成 DDR3 IP 核的界面中,可以找到 User Guide 手册,DDR3 的使用将围绕这个手册来展开。

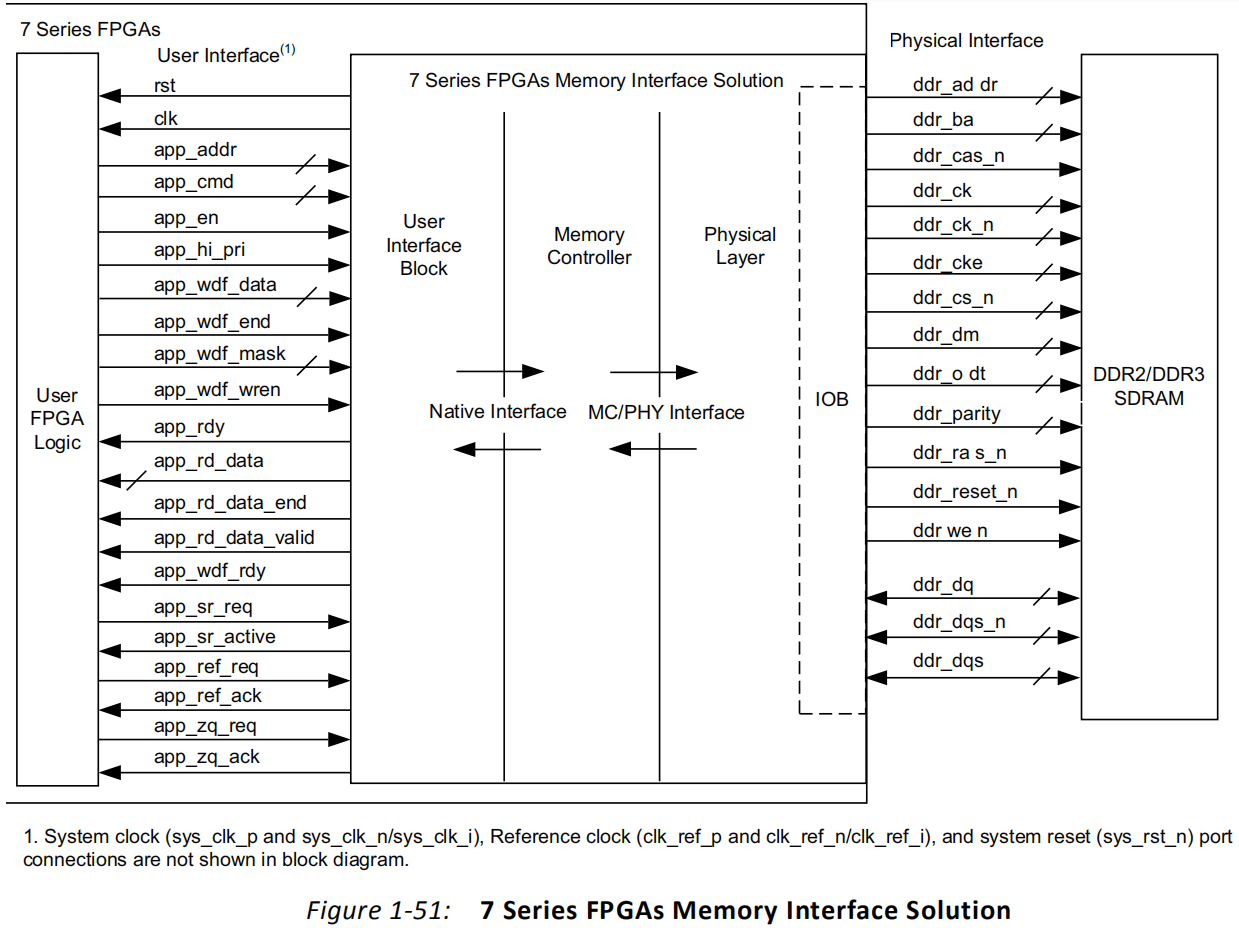

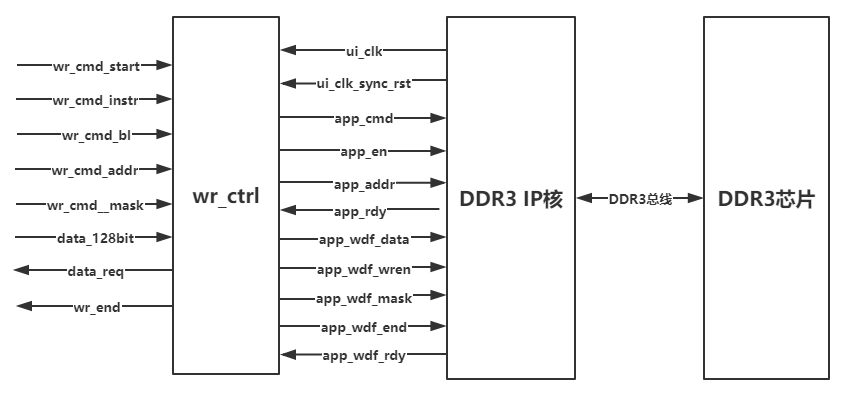

一、接口框图

打开 User Guide 第 90 页,可以看到 DDR3 IP 核的接口框图如下所示。可以看到,中间部分就是我们调取的 DDR3 IP 核,它预留了两组总线,右边一组直接绑定在 DDR3 芯片端口,其总线信号名称均以 ddr 开头,这部分总线只需要在 top 层设为端口即可,无需自己写代码控制。而左边一组则是留给用户端逻辑,其总线信号名称多以 app 开头,这些信号则需我们自己来编写实现。

二、总线详解

对于 User Interface用户端逻辑信号, User Guide 第92页里有个汇总表,我们简单翻译一下。

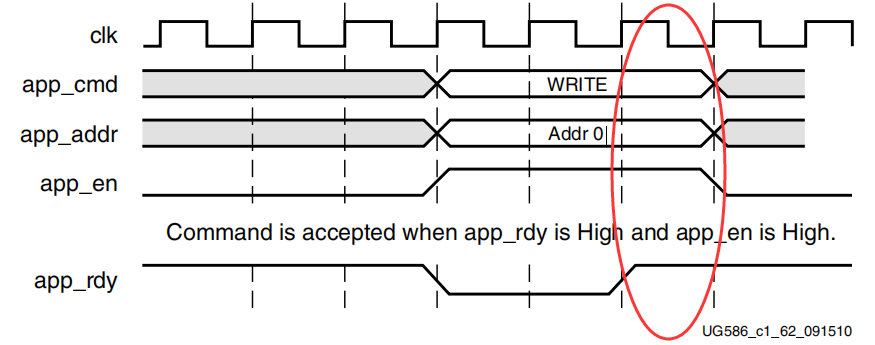

1、命令总线(表格红色部分),其时序图如下所示。

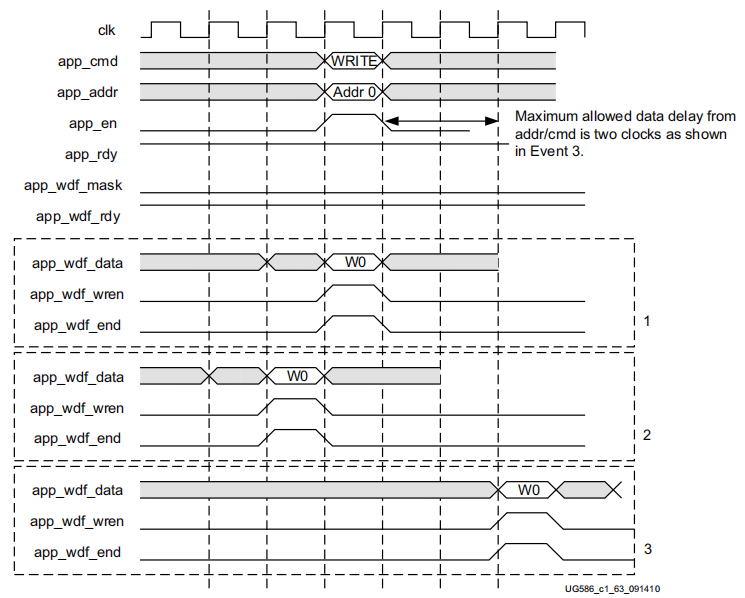

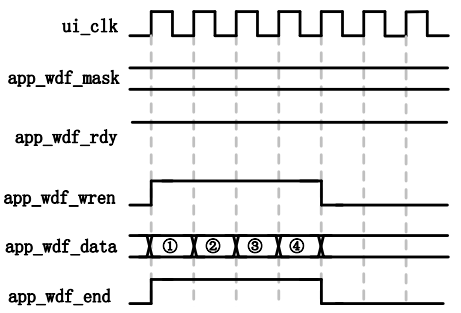

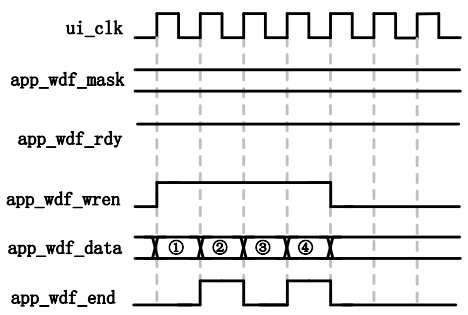

2、写总线(表格黄色部分),其时序图如下所示。共有 3 种传输模式。模式 1 指的是命令和数据同时发送到 IP 核,模式 2 指的是数据提前于命令发送到 IP 核,模式 3 指的是数据落后于命令发送到 IP 核。模式 1 和 2 均可稳定传输,而模式 3 必须满足一个条件,即数据落后命令的时间不能超过两个时钟周期。一般来说,模式 2 比较常用,时序设计相对容易。

关于 app_wdf_end 信号,该信号表示:当前突发写的最后一个数据。在A7 DDR3 的控制器IP核中,只存在突发长度为 8 地址的形式 ,1 个地址能存放的数据是 16bit,因此每一次的地址突发带来的数据突发为 8*16=128 bit(对外接口为128bit)。本次 DDR3 IP 核调取时,我们选取的 “物理层 - 用户端” 的速率为 4:1,每次发送的有效数据为 128 bit,因此1 次突发写就完成了数据的写入,app_wdf_end 和 app_wdf_en 时序上同步了。

而如果选取的 “物理层 - 用户端” 的速率为 2:1,每次发送的有效数据为 64 bit,因此1次突发要分成2次才能真正写完,app_wdf_end 就看得更清楚了。

3、读总线(表格黄色部分),也分为两种速率,4:1 和 2:1。

4、其他总线(表格白色部分)

本次设计没有使用到,不作讲解。

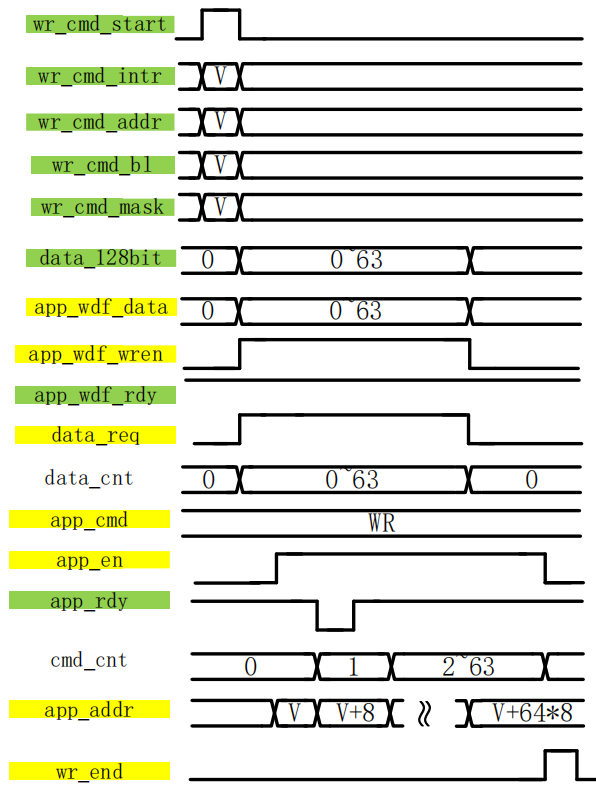

三、写控制模块设计

本次设计写控制模块,试着将64个128bit数据写入DDR3 IP核,并最终进行仿真验证。为什么是64个?因为我喜欢。写控制模块框图如下所示:

当 wr_cmd_start 有效时启动本次的突发写,根据外部输入信号 wr_cmd_bl 可以确定本次突发需要写多少个数据。wr_cmd_addr 代表本次突发写的起始地址,数据是128bit的,一个地址能存16bit,因此每个128bit数据需要占用8个地址,即每次的地址计数+8。wr_end 用于告知其他模块,本次突发写结束。

本次设计均学自《威三学院FPGA教程》,具体代码就不贴了。

顶层文件不要忘了例化此模块。

//写控制模块 ---------------------------------------------------------------

wr_ctrl u_wr_ctrl

(

.sclk (ui_clk ), // input 100Mhz

.rst (ui_clk_sync_rst | (~init_calib_complete)), // input

.wr_cmd_start (wr_cmd_start ), // input

.wr_cmd_instr (wr_cmd_instr ), // input [ 2:0]

.wr_cmd_bl (wr_cmd_bl ), // input [ 6:0]

.wr_cmd_addr (wr_cmd_addr ), // input [27:0]

.wr_cmd_mask (wr_cmd_mask ), // input [15:0]

.data_128bit (data_128bit ), // input [127:0]

.data_req (data_req ), // output

.wr_end (wr_end ), // output

.app_rdy (app_rdy ), // input

.app_wdf_rdy (app_wdf_rdy ), // input

.app_en (app_wr_en ), // output

.app_addr (app_wr_addr ), // output [27:0]

.app_cmd (app_wr_cmd ), // output [ 2:0]

.app_wdf_mask (app_wdf_mask ), // output

.app_wdf_wren (app_wdf_wren ), // output

.app_wdf_data (app_wdf_data ), // output [127:0]

.app_wdf_end (app_wdf_end ) // output

);

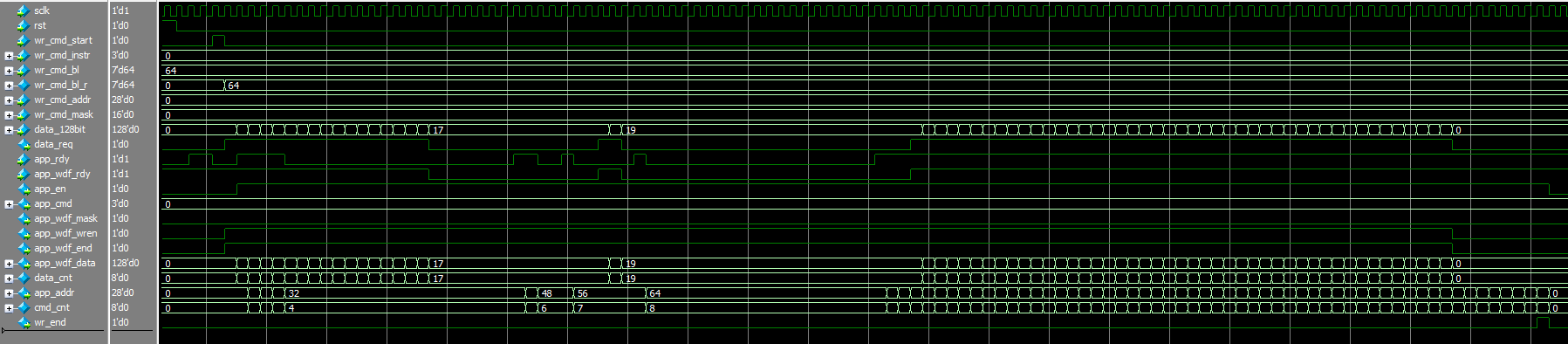

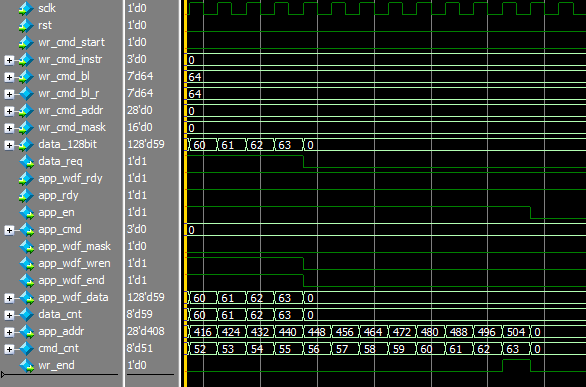

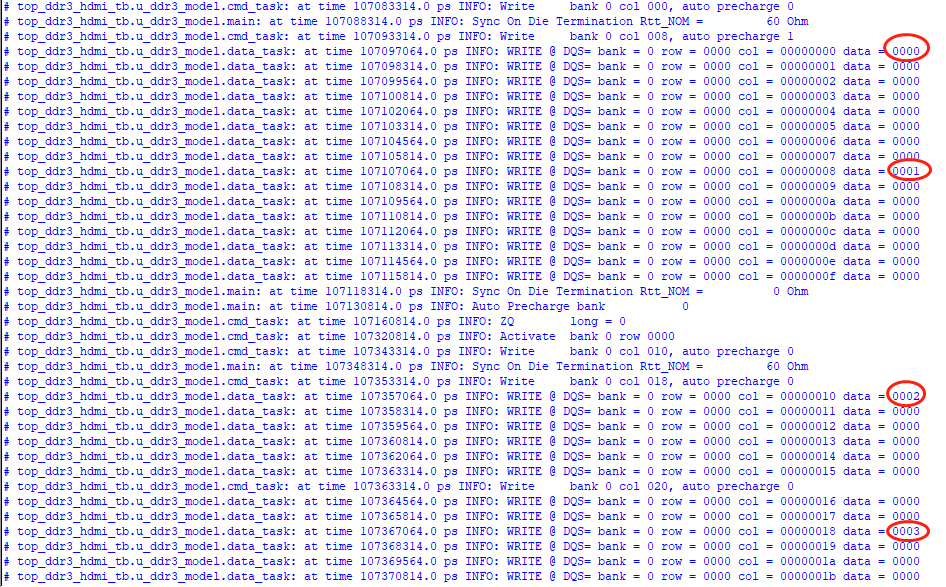

四、写控制模块仿真

可以看出,数据成功写入到了 ddr3 ip核。

调试 Modelsim 小技巧:在sim --- sim_1 --- behav --- modelsim中打开 top_ddr3_hdmi_tb_compile.do 文件,将最后一句 quit -force 删除掉,即可不关闭 Modelsim 调试仿真。

参考资料:威三学院FPGA教程

最新文章

- Safari 快捷键

- JavaScript基础——理解变量作用域

- Selenium2学习-038-firefox、webdriver版本不对称问题解决:org.openqa.selenium.firefox.NotConnectedException: Unable to connect to host 127.0.0.1 on port 7055

- 看了让人笑了很多很多次的NB的痔疮经历

- python PIL安装

- pfx,cer转pem,并对通过pem文件进行签名与验签

- 【转】C# 后台开启 cmd执行命令

- useradd adduser linux创建用户、设置密码、修改用户、删除用户

- 在ubuntu纯字符gdb界面下来开发调试嵌入式ARM

- Python os模块--路径、文件、系统命令等操作

- localstorage本地定时缓存

- JAVA入门[3]—Spring依赖注入

- eclipse每次闪退后都提示查看\workspace\.metadata\.log

- Css中的盒子结构padding和margin的区别

- Mybatis 系列9

- iOS开发简记(9):APPStore审核

- ECC加密算法入门介绍 --- 看雪

- Springboot多数据源配置--数据源动态切换

- ELK基础原理

- 给<input type="color">设置默认值