xilinx fpga 生成3*3窗口

2024-08-30 01:04:33

在写滤波程序的时候在网上看了好几篇大佬的笔记,都有提到使用3*3窗口,由于小白一个,看到复杂的理论就惧怕的不行。但是现在不得不上,自己调用移位寄存器ip核然后做了个3*3窗口出来,自己动手作出来忽然感觉到也不难嘛。

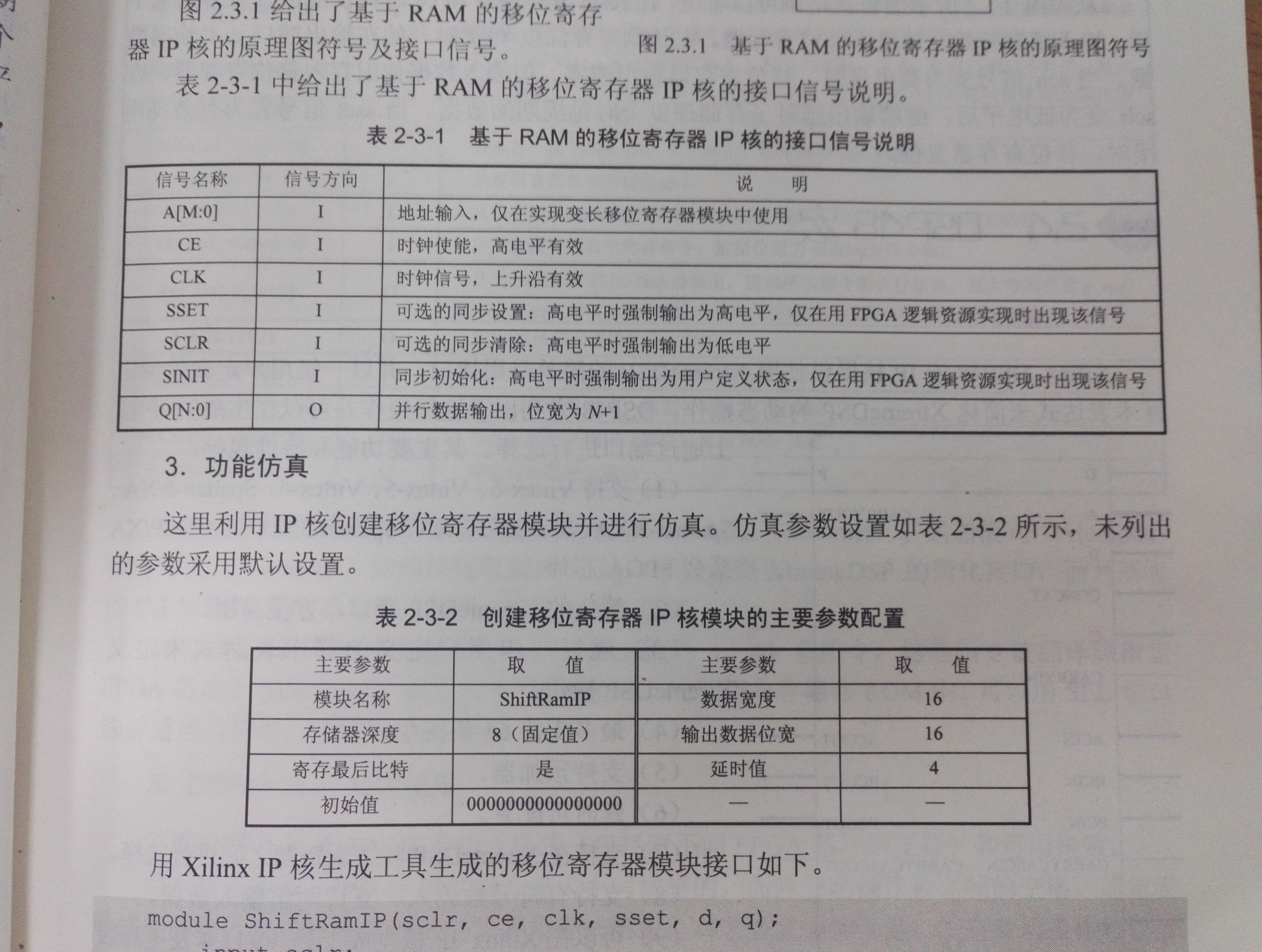

先贴一张ip核模块的接口参数图

生成3*3窗口需要两个寄存器,参数设置为数据宽度8,深度一个为4,另一个为3,选sclr端口

然后把两个移位寄存器串联起来就可以了

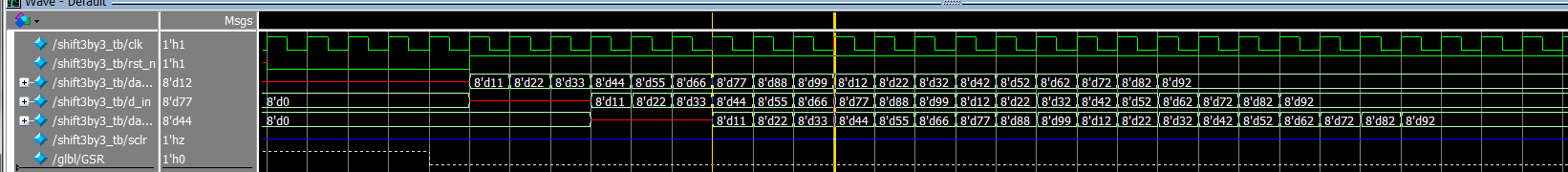

仿真的时候写好激励就行

放上最后仿真图

两条线那会是不是3*3矩阵呀,然后往右推就行。

顶层模块

module shift3by3(

clk,

rst_n,

datain,

dataout

);

input clk;

input rst_n;

input [:] datain;

output [:] dataout; wire [:] d_in;

wire sclr; shiftip shift2(

.clk(clk),

.sclr(~rst_n),

.d(datain),

.q(d_in)

); shift3 shift3(

.clk(clk),

.sclr(~rst_n),

.d(d_in),

.q(dataout)

); endmodule

tesrbench

module shiftiptb;

// Inputs

reg clk;

reg [:] d;

// Outputs

wire [:] q;

// Instantiate the Unit Under Test (UUT)

shiftip uut (

.clk(clk),

.d(d),

.q(q)

);

initial clk=;

always # clk=!clk;

initial begin

// Initialize Inputs

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

# d=;

// Wait 100 ns for global reset to finish

#;

// Add stimulus here

end

endmodule

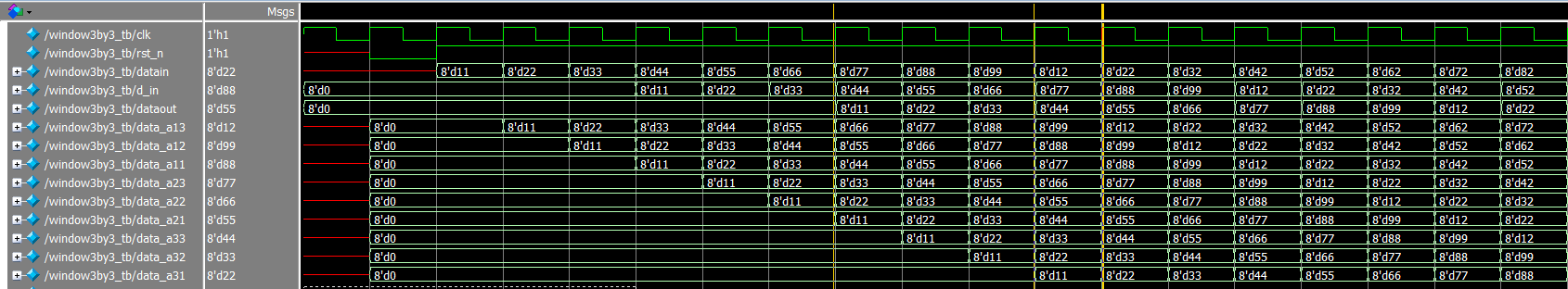

之前没有将矩阵里的9个元素列出来,现在将9个元素列出来,

赋值代码如下:

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

{a11,a12,a13} <= {'b0,8'b0,'b0};

{a21,a22,a23} <= {'b0,8'b0,'b0};

{a31,a32,a33} <= {'b0,8'b0,'b0};

row <= 'b0;

end

else

begin

row <= row3;//row3就是datain,这里延迟一个时钟

{a11,a12,a13} <= {a12,a13,row};

{a21,a22,a23} <= {a22,a23,row2};//row2是d_in

{a31,a32,a33} <= {a32,a33,row1};//row1是dataout

end

仿真图像如下图所示:

最新文章

- 升级xcode8 之后遇到的一些问题

- TF-IDF算法学习报告

- sql 的实用函数(包含日期函数、截取字符串函数)

- 在IDEA 上使用Git查看主干和分支等

- css3和原生js时钟

- 线程——QQ邮件发送

- 【JavaScript】 2013年度最强AngularJS资源合集

- NUMA

- 转:PHP开发者应了解的24个库

- Shell中特殊的变量

- 免费邮件服务器:MailEnable

- 操作数据表中的记录——SELECT (where表达式、GROUP BY、HAVING、LIMIT)

- ASP.NET - 出错页

- C和C++中的名字空间和作用域

- 深入Java关键字instanceof

- 「雅礼集训 2017 Day5」矩阵

- linux 软链接和硬链接的区别 和 inode 的理解

- Jmter接口网站压力测试工具使用记录

- windows下彻底删除jenkins

- windows下一分钟配置ngnix实现HLS m3u8点播