简易APB4 slave实践

2024-08-22 07:59:28

一个简易的(不完整的)APB4 slave的可以没有PREADY和PSLVERR,这两个信号都被赋予常数,以及没有PPROT。

两种不同类型的寄存器:

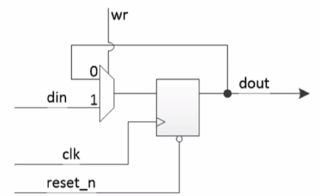

图: 普通寄存器电路图

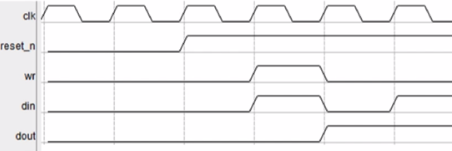

图: 带读写控制寄存器电路图

图:带读写控制寄存器时序图

一般来讲,一个模块的interface到内部reg之间,需要的信号为地址信号addr,读写使能信号(分开),byte_strobe字节选通信号,读写数据信号(分开)。

注意:在传输结束后不要立即更改地址和写信号,保持当前状态知道开始下一个传输,这样可以降低功耗。

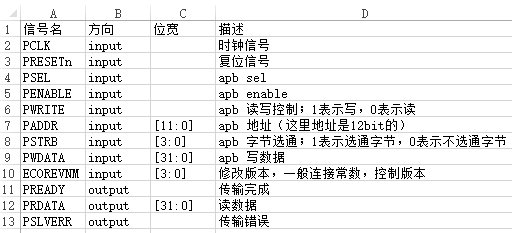

interface spec:

寄存器表:

代码:apb4的顶层

module apb4_slave #(

parameter ADDRWIDTH = )

(

input wire PCLK,

input wire PRESETn, input wire PSEL,

input wire[ADDRWIDTH -:] PADDR,

input wire PENABLE,

input wire PWRITE,

input wire[:] PWDATA,

input wire[:] PSTRB, input wire[:] ECOREVNUM, output wire[:] PRDATA,

output wire PREADY,

output wire PSLVERR

);

wire [ADDRWIDTH-:] reg_addr;

wire reg_read_en;

wire reg_write_en;

wire [:] reg_byte_strobe;

wire [:] reg_wdata;

wire [:] reg_rdata;

apb4_slave #(.ADDRWIDTH (ADDRWIDTH))

u_apb_slave_interface(

.pclk (PCLK),

.presetn (PRESETn), .psel (PSEL),

.paddr (PADDR),

.penable (PENABLE),

.pwrite (PWRITE),

.pwdata (PWDATA),

.pstrb (PSTRB), .prdata (PRDATA),

.pready (PREADY),

.pslverr (PSLVERR), .addr (reg_addr),

.read_en (reg_read_en),

.write_en (reg_write_en),

.byte_strobe (reg_byte_strobe),

.wdata (reg_wdata),

.tdata (reg_rdata) );

如何在interface这个模块中确定APB的建立周期信号?

其实APB的建立周期信号可以理解为一个使能信号,在第一周期拉高这个使能信号,那么下个周期就可以判断使能信号,并进入到传输周期了。这里使用组合逻辑去解决使能信号问题,一个是读使能read_en,一个是写使能write_en。read_en = psel &(~pwrite); write_en = psel &(~penable) & pwrite; 这里peanble是主机发过来的输入信号,这里说的从机不用管。

代码:apb4的逻辑接口

u_apb_slave_interfacef #(

parameter ADDRWIDTH = )

(

// IO declaration

input wire pclk,

input wire presetn,

// apb interface input

input wire psel,

input wire[ADDRWIDTH-:] paddr,

input wire penable,

input wire pwite,

input wire[:] pwdata,

input wire[:] pstrb,

// apb interface output

output wire[:] prdata,

output wire pready,

// Register interface

output wire[ADDRWIDTH-:] addr,

output wire read_en,

output wire write_en,

output wire[:] byte_pstrb,

output wire[:] wdata,

output wire[:] rdata

); assign pready = 'b1;

assign pslverr = 'b0; assign addr = paddr;

assign read_en = psel & (~pwrite); // 当pwrite为0,psel为1的时候,才读

assign write_en = psel & (~penable) & pwrite; // 在PCLK中,第一拍为psel有效,penable为低,第二拍才是psel和penable同时有效; assign byte_pstrb = pstrb;

assign wdata = pwdata;

assign prdata = rdata;

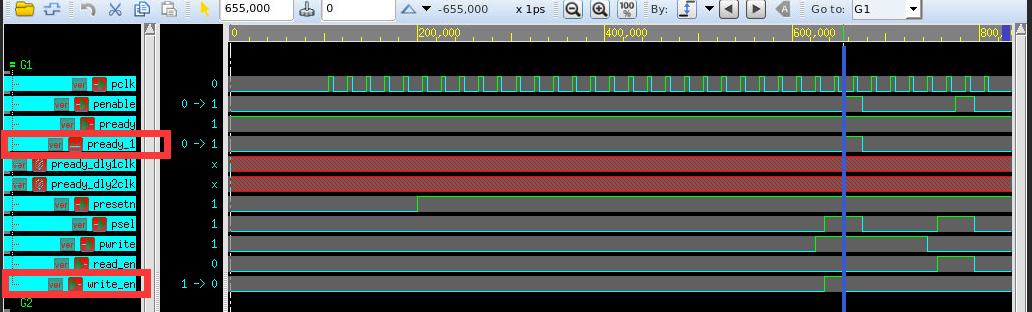

如何设计有等待状态的写传输?

从模块的pready输出之前一直是高,现在想延迟一个时钟周期,做成脉冲形式。

可以使用组合逻辑如:

assgin pready_1 = psel & peanble & pwrite;

pready想延迟多个时钟节拍,可以使用时序电路,建立周期完成后,等待多个clock之后,再讲pready拉高。

代码:apb的寄存器读写

module apb4_slave_reg #(

parameter ADDRWIDTH = )

(

input wire pclk,

input wire presetn, input wire[ADDRWIDTH-:] addr,

input wire read_en,

input wire write_en,

input wire[:] byte_pstrb,

input wire[:] wdata,

input wire ecorevnum,

output wire[:] rdata ); localparam ARM_CMSDK_APB4_EG_SLAVE_PID4 = 'h00000004; // 12'hFD0;

localparam ARM_CMSDK_APB4_EG_SLAVE_PID5 = 'h00000000; // 12'hFD4;

localparam ARM_CMSDK_APB4_EG_SLAVE_PID6 = 'h00000000; // 12'hFD8;

localparam ARM_CMSDK_APB4_EG_SLAVE_PID7 = 'h00000000; // 12'hFDC;

localparam ARM_CMSDK_APB4_EG_SLAVE_PID0 = 'h00000019; // 12'hFE0;

localparam ARM_CMSDK_APB4_EG_SLAVE_PID1 = 'h000000B8; // 12'hFE4;

localparam ARM_CMSDK_APB4_EG_SLAVE_PID2 = 'h0000001B; // 12'hFE8;

localparam ARM_CMSDK_APB4_EG_SLAVE_PID3 = 'h00000000; // 12'hFEC; wire [:] wr_sel; // 取地址的高10位出来,地址是4K对其的,之后高12bits是不一样的,从0xfff~0x000,其中的高10位就可以判断出是要操作那个寄存器了

// 地址是32为对其的,末尾都是0(0000)、4(0100)、8(1000)、C(1100)循环的,低两位都是一样的,只有高10位不一样

assign wr_sel[] = ((addr[(ADDRWIDTH-):]=='b0000000000)&(write_en)) ? 1'b1: 'b0;

assign wr_sel[] = ((addr[(ADDRWIDTH-):]=='b0000000001)&(write_en)) ? 1'b1: 'b0;

assign wr_sel[] = ((addr[(ADDRWIDTH-):]=='b0000000010)&(write_en)) ? 1'b1: 'b0;

assign wr_sel[] = ((addr[(ADDRWIDTH-):]=='b0000000011)&(write_en)) ? 1'b1: 'b0; // write_en = psel & (~penable) & pwrite; 时序要求在penable为高这一拍把数据写下去,所以要在其前一拍判断是否要写。 // 寄存器的写操作

// Data register: data0

always @(posedge pclk or negedge presetn) begin

if (~presetn) begin

data0 <= {{'b0}};

end

else if (wr_sel[]) begin

if (byte_strobe[])

data0[ :] <= wdata[:];

if (byte_strobe[])

data0[:] <= wdata[:];

if (byte_strobe[])

data0[:] <= wdata[:];

if (byte_strobe[])

data0[:] <= wdata[:];

end

end

// Data register: data1

always @(posedge pclk or negedge presetn) begin

if (~presetn) begin

data1 <= {{'b0}};

end

else if (wr_sel[]) begin

if (byte_strobe[])

data1[ :] <= wdata[:];

if (byte_strobe[])

data1[:] <= wdata[:];

if (byte_strobe[])

data1[:] <= wdata[:];

if (byte_strobe[])

data1[:] <= wdata[:];

end

end

// Data register: data2

always @(posedge pclk or negedge presetn) begin

if (~presetn) begin

data2 <= {{'b0}};

end

else if (wr_sel[]) begin

if (byte_strobe[])

data2[ :] <= wdata[:];

if (byte_strobe[])

data2[:] <= wdata[:];

if (byte_strobe[])

data2[:] <= wdata[:];

if (byte_strobe[])

data2[:] <= wdata[:];

end

end

// Data register: data3

always @(posedge pclk or negedge presetn) begin

if (~presetn) begin

data3 <= {{'b0}};

end

else if (wr_sel[]) begin

if (byte_strobe[])

data3[ :] <= wdata[:];

if (byte_strobe[])

data3[:] <= wdata[:];

if (byte_strobe[])

data3[:] <= wdata[:];

if (byte_strobe[])

data3[:] <= wdata[:];

end

end // 寄存器的读操作

always @(read_en or addr or data0 or data1 or data2 or data3 or ecorevnum) begin

case (read_en)

'b1: begin

if (addr[:] == 'h00) begin // 判断为RW类型的寄存器

case (addr[:])

'b00: rdata = data0;

'b01: rdata = data1;

'b10: rdata = data2;

'b11: rdata = data3;

default: rdata = {{'bx}};

endcase

end

else if (addr[:] == 'h3F) begin // 判断为RO类型的寄存器

case(addr[:])

'b0100:rdata = ARM_CMSDK_APB4_EG_SLAVE_PID4;

'b0101:rdata = ARM_CMSDK_APB4_EG_SLAVE_PID5;

'b0110:rdata = ARM_CMSDK_APB4_EG_SLAVE_PID6;

'b0111:rdata = ARM_CMSDK_APB4_EG_SLAVE_PID7;

'b1000:rdata = ARM_CMSDK_APB4_EG_SLAVE_PID0;

'b1001:rdata = ARM_CMSDK_APB4_EG_SLAVE_PID1;

'b1010:rdata = ARM_CMSDK_APB4_EG_SLAVE_PID2;

'b1011:rdata = {ARM_CMSDK_APB4_EG_SLAVE_PID3[31:0],ecorevnum[3:0],4'h0};

default: rdata = {{'bx}};

endcase

end

else begin

rdata = {{'b0}};

end

end

'b0: begin

rdata = {{'b0}};

end

default: rdata = {{'bx}};

endcase

end endmodule

最新文章

- 【php爬虫】百万级别知乎用户数据爬取与分析

- [PCL]点云渐进形态学滤波

- 黄聪:《跟黄聪学WordPress插件开发》

- [webgrid] – header - (How to Add custom html to Header in WebGrid)

- MFC编程入门之十(对话框:设置对话框控件的Tab顺序)

- wp7 中 HubTile控件自定义大小。

- [SAP ABAP开发技术总结]Function远程、同步、异步调用

- CSS样式鼠标点击与经过的效果一样

- HTTP BIN测试

- 【C++继承与派生之二】有子对象的派生类的构造函数

- mssql分页原理及效率分析

- 1,fiddler的工作原理和安装

- CSS3动画属性:动画(animation)

- SQL Server 备份到网络盘网络映射盘

- 求助Ubuntu16.10如何设置默认启动为字符界面

- 一个能够编写、运行SQL查询并可视化结果的Web应用:SqlPad

- oracle 按照时间间隔进行分组

- mysql优化连接数

- 你都掌握了吗?jQuery 选择器大全

- m2014-architecture-imgserver->配置lighttpd mod_mem_cache 模块做静态资源服务器